# Safety assurance of an industrial robotic control system using hardware/software co-verification

Yvonne Murray<sup>a,</sup>, Martin Sirevåg<sup>a</sup>, Pedro Ribeiro<sup>b</sup>, David A. Anisi<sup>a,c</sup>, Morten Mossige<sup>d</sup>

<sup>a</sup>Dept. of Mechatronics, Faculty of Engineering and Science, University of Agder (UiA), Norway <sup>b</sup>Dept. of Computer Science, University of York, UK <sup>c</sup>Robotics Group, Faculty of Science & Technology, Norwegian University of Life Sciences (NMBU), Norway <sup>d</sup>ABB Robotics, Bryne, Norway

# Abstract

As a general trend in industrial robotics, an increasing number of safety functions are being developed or re-engineered to be handled in software rather than by physical hardware such as safety relays or interlock circuits. This trend reinforces the importance of supplementing traditional, input-based testing and quality procedures which are widely used in industry today, with formal verification and model-checking methods. To this end, this paper focuses on a representative safety-critical system in an ABB industrial paint robot, namely the High-Voltage electrostatic Control system (HVC). The practical convergence of the high-voltage produced by the HVC, essential for safe operation, is formally verified using a novel and general co-verification framework where hardware and software models are related via platform mappings. This approach enables the pragmatic combination of highly diverse and specialised tools. The paper's main contribution includes details on how hardware abstraction and verification results can be transferred between tools in order to verify system-level safety properties. It is noteworthy that the HVC application considered in this paper has a rather generic form of a feedback controller. Hence, the co-verification framework and experiences reported here are also highly relevant for any cyber-physical system tracking a setpoint reference.

*Keywords:* Formal Verification, Co-Verification, Model Checking, High-Voltage Controller (HVC), Robots, Cyber-Physical Systems (CPS)

#### 1. Introduction

The liberation of industrial robots from traditional metal cages and steadily increasing number of co-bots working side by side with humans are illustrative examples of a general trend in industrial robotics. In the wake of this, more and more safety-critical functions are now being developed to be handled by software and/or firmware components instead of hardware safety relays or interlock circuits. Modern industrial robots are heavily dependent on software-implemented safety signals to monitor and control various critical subsystems such as current/voltage supervision and emergency stop or short circuit interrupts. This trend brings several distinctive advantages such as cost-reduction and increased flexibility. Nevertheless, it also introduces or reinforces negative side-effects, most notably in the form of higher system complexity, vulnerability and dependability [1].

To set the stage for and address this ongoing industrial trend, this paper advocates use of formal verification techniques, which can provide an extra level of assurance by verifying the logic of a system. The application of formal methods in the robotics industry will ideally help to identify potential pitfalls at a much earlier phase of the development cycle [2] and serve as an important supplement to the traditional testing

*Email addresses:* yvonne.murray@uia.no (Yvonne Murray), martin.sirevag@uia.no (Martin Sirevåg), pedro.ribeiro@york.ac.uk (Pedro Ribeiro), david.anisi@nmbu.no (David A. Anisi), morten.mossige@no.abb.com (Morten Mossige)

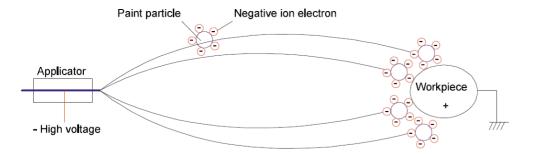

Figure 1: In electrostatic painting, high-voltage (approximately 40-90 kV) charges the paint particles at the applicator. The particles follow the lines of the electrostatic field from the applicator (cathode) to the earthed workpiece (anode).

and safety risk identification and mitigation actions which are already employed [3]. Obtaining sufficiently high testing coverage in complex industrial systems can be time-consuming and expensive. In practice, it is most often not viable to account for every scenario, which means that testing can fail to reveal potential safety-critical issues.

The HVC system considered in this paper provides a perfect example of this. As described in [4], a previous version of the HVC software (SW) has been shown to contain some errors, e.g., failure to properly follow the given setpoint. These errors are described in more detail in [4] and went undetected despite passing rigorous and certified quality assurance and testing procedures. These included *a priori* and systematic identification of risk mitigation plans (e.g., using HAZID/HAZOP), as well as thorough testing procedures consisting of static code analysis, unit testing, component testing and system test I and II. Here, system test I encompasses hardware tests with the Integrated Painting System (IPS) and HVC active, while system test II entails testing of the entire robotic system using actual paint.

The robotic spray booth in, e.g., a car factory, may contain flammable solvent and paint particles in the air. Hence, paint robots are certified for operation in potentially explosive atmospheres in accordance with regional ATEX/NFPA/IECEx standards (ATEX Directive – 2014/34/EU, IEC 60079). The paint version of the ABB Industrial Robot Controller unit, denoted IRCP, is certified with respect to the ISO 10218 standard for safety requirements for industrial robots. Paint robots using HVC are also certified according to the EN50176 standard for using high-voltage in explosive environments, while the paint atomizer is certified in accordance to ISO 9001 and ISO 14001.

Industrial paint robots use high-voltage to perform electrostatic painting, where particles are electrically charged and attracted to the grounded paint object, as seen in Fig. 1 [5, 6]. In this way, painting quality is ensured while paint consumption and costs are minimized. However, the use of high-voltage also poses certain risks of electric shock and ignition. Fire in the painting cell may result in costly production delays, as well as damage to the equipment. Therefore, it is of great importance that the HVC works as intended.

The HVC example illustrates the fact that the complete elimination of all errors is most often not practical (due to cost and/or time constraints) or even possible. Formal verification provides us not only with a mathematically sound formalism for the specification and verification of robotic systems which ensures correctness, but also provides evidence for safety certification purposes. In fact, a survey on safety-critical robot systems [1] recognises formal verification and correct-by-construction control synthesis as two main areas needed to develop safe robot systems.

Robot control systems, like the HVC, have rather natural and generic properties that are expected to be fulfilled by any feedback controller tracking a setpoint reference. Formally verifying that overall the setpoint is followed, a system property, however, requires reasoning over the combined, time-dependent behaviour of software and hardware. For pragmatic reasons these are often modelled using diverse languages and formalisms, making holistic reasoning challenging.

Inspired by co-simulation approaches [7], in this paper we propose a novel and generic co-verification

approach for pragmatic verification of system properties. Models of the software and hardware are coupled through platform mappings that define how the inputs and outputs of the software are connected to those of the hardware, in terms of its sensors and actuators. With our approach, behavioural properties of individual models – that may be established using separate domain-specific tools – can be combined to support the verification of system properties, using practical techniques, such as model checking [8].

To illustrate the use of co-verification in a representative industrial case study, the HVC software is modelled in RoboChart [9, 10, 11], while the hardware is modelled in Simulink [12]. RoboChart is a domain-specific language for model-based software engineering of robotics, with a formal semantics encompassing timed and functional aspects, that is tailored for formal verification. Simulink, on the other hand, is a *de facto* standard for control engineering, as typically used in industry for dynamic simulation. For co-verification we use the MathWorks Simulink Design Verifier (SDV) toolbox [12], and the CSP model-checker FDR [13], as integrated into RoboTool [9, 10, 11].

Importantly, we demonstrate the value of our approach in identifying errors that existed in an early-phase HVC software version as described in [4]. In the next phase, once the identified software shortcomings had been rectified, we were able to show that it satisfies all safety properties of concern. Namely, that overall the system tracks the high-voltage setpoint as set by an operator, and that the software resets the setpoint and disables the high-voltage if it senses that the power supply is unstable. This serves as a testimony of the strength and suitability of using formal verification methods for industrial safety-critical systems.

Some initial and preliminary results of our work regarding formal verification of HVC of industrial paint robot have been previously published in [4]. This paper extends that work by addressing some fundamental and important aspects, most notably by:

- 1. taking into account the timed aspects of the HVC controller using the timed semantics of RoboChart.

- 2. replacing the simplified, binary representation of the output voltage *following* the setpoint, with a real representation and considering timed and dynamic *convergence* towards the setpoint signal.

- 3. providing a crisp dichotomy between control software and physical hardware parts of the HVC system, together with detailed platform mapping in-between [14, 15].

- 4. modelling the system dynamics of the hardware in Simulink [5, 6].

- 5. using a novel approach to co-verification to combine the results from hardware simulations in Simulink with the model-checking capabilities of RoboTool [16] to verify that the high-voltage produced by the HVC follows the setpoint, a system-level safety property.

The remainder of this paper is structured as follows. Section 2 discusses related work. Section 3 provides an overview of the HVC system, contains formulations of the properties to be formally verified (Section 3.1) and presents a simplified finite state machine of the HVC (Section 3.2). Section 4 constitutes the main body of the current paper. It details the co-verification framework and explains how the state machine was modelled in RoboChart and combined with Mathworks SDV simulation and verification results in order to verify the system-level safety property concerning the high-voltage. Section 5 reports on the verification of software properties. Finally, Section 6 provides some discussion and conclusions, as well as suggestions for further research.

## 2. Related Work

The survey on safety-critical robot systems in [1] identifies seven areas that need further focus and research in order to develop safe, dependable robotic systems. It is notable that at least five of these areas are relevant in the context of this paper, namely: adaptive safety monitoring, modeling and simulation for safety analysis, formal methods for verification, correct-by-construction control, and certification.

A recent survey [17] maps and lists the current challenges, used formalisms, tools, approaches, as well as limitations when considering formal specification and verification of autonomous robotic systems. The main results reveal that temporal logic, state-transition and model checking are the main formalisms and approaches used during the last decade. At the same time, the lack of appropriate tools and sheer resistance to adopting formal verification methods in robotic systems development are recognised as the main limiting factors for wider impact. Likewise, the lack of interoperability and need to capture the essence of complex, industrial robotic systems using several formalisms and tools is recognised.

Simulation plays an important role in the development of robotic systems, and more widely in the domain of cyber-physical systems (CPS). However, current practice makes it difficult to soundly reason across models of the software, simulation, and hardware, which can exacerbate the reality gap. Co-simulation approaches [7, 18] bridge the heterogeneity of tools via orchestration, for example, using a common API as advocated in the FMI standard [19]. Besides the issue of code portability between tools, robotics simulators [20] tend to use different physics engines. A related approach [15] to our work on co-verification, extends the diagrammatic simulation language RoboSim [21] with facilities to cover physical modelling of robotics and establish formal links between sensors, actuators, and the software, via platform mappings.

Kawahara et al. [22] address the co-simulation of Simulink and a subset of SysML [23], where data is exchanged between models via input/output ports modelled as S-Functions in Simulink. Their focus is on testing of simulations against timed constraints expressed via sequence diagrams using the UML-MARTE [24] profile. Cavalcanti et al. [18] give semantics to a version of INTO-SysML [25], a SysML profile suitable for co-simulation using FMI, where RoboChart is used with Simulink in the co-simulation of a chemical detector robot. Bernardeschi et al. [26] use timed automata, encoded for reasoning in the PVS theorem prover [27], in co-simulation with a Simulink model of a cardiac pacemaker. Our focus, however, is on (co-)verification.

Recognising the broad range of aspects in the engineering of robots, the use of specialised, and complementary, verification techniques is widely reported in the literature. Webster et al. [28] propose a "corroborative" approach where agreement is sought between different verification techniques with respect to functional requirements, including model checking with PRISM [29], simulation-based testing and user validation.

Cardoso et al. [30] use different methods to verify components of a simulation of NASA's Curiosity rover, where high-level control is driven by a Beliefs-Desires-Intentions (BDI) agent. The agent is verified using the Agent Java Path Finder (AJPF) model checker [31], while its interface with the environment is verified using Dafny [32]. FDR is used to verify a CSP model of the action library nodes that implement control methods following the publish-subscribe paradigm of the Robot Operating System (ROS) [33]. The emphasis is on verification of components with formal models guiding the generation of runtime monitors.

Related, Bourbouh et al. [34] report on the combined use of several methods and tools in the development of an assurance case for an inspection rover, which is modelled in AADL [35], Simulink and Event-B [36]. Functional requirements are stated using the structured natural language accepted by FRET [37], with semantics given in Linear Temporal Logic (LTL) suitable for analysis with Lustre [38] models generated from Simulink via CoCoSim [39], a framework for design, code generation and analysis of discrete dataflow models. Simulink blocks modelling the rover architecture are annotated with assume-guarantee contracts based on component requirements formalised in FRET. System-level properties are then verified via model checking with Kind2 [40], while some components are verified using Event-B instead.

The literature is rich in approaches for formal verification of Simulink models. Reicherdt and Glesner [41] propose translating discrete-time Simulink models into Boogie [42] for verifying the absence of common error classes, such as overflows, underflows, division-by-zero and range violations. CoCoSim follows on from previous work [43] targeting Lustre and SCADE [44]. Boström and Wiik [45] propose a compositional approach for verifying Simulink blocks annotated with assume-guarantee contracts.

Applications of formal verification methodologies within the control and CPS community have mainly adopted the hybrid system and automata framework of Alur et al. [46, 47]. In this setting, finite- and infinite-time reachability constitute the main verification tools, but unfortunately turn out to be an undecidable problem in general, leaving conservative set approximation as the only viable approach [48, 49]. Hybrid automata also assumes having infinite accuracy and instantaneous reaction which serves as a noticeable discrepancy to the real system and implementation; potentially invalidating the verification results [50].

Focusing on formal verification of industrial robot applications, in [3], industrial robot- and PLCprograms are compiled into PROMELA models as input for the SPIN model checker [51]. The work is however restricted to LTL formulas. It further differs from our work by solely considering deadlocks, collisions and kill-switch violations. Narrowing down to industrial paint robots, [52] considers formal verification

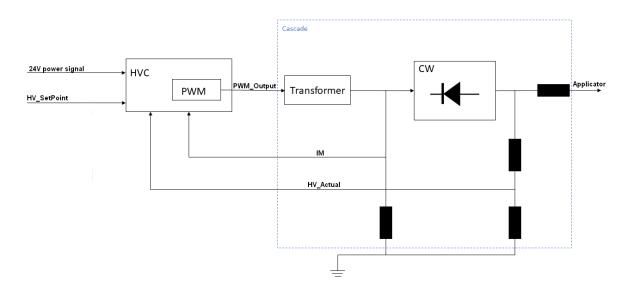

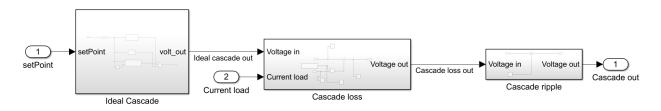

Figure 2: Block diagram of one part of the paint robot, containing the HVC.

of paint spraying using the ARIADNE tool for reachability analysis. The focus here is solely on parametric design verification.

# 3. High-Voltage Control (HVC)

A simplified block diagram of the HVC part of the paint robot can be seen in Fig. 2. The HVC module runs the control software loops and associated control logic. Here, the  $r(t) = HV\_SetPoint$  signal is a function of time, t, and used as a priori given reference for the desired voltage level on the HVC, while the 24V power signal provides the HVC with electrical power. The  $u(t) = PWM\_Output$  signal serves as input signal to the Pulse Width Modulation (PWM) hardware. It is a percentage, from 0 to 100%, mapped to an analog 0 to 10 voltage signal, which is then increased in the transformer. In the Cockcroft–Walton (CW) cascade generator, there are several voltage doubling circuits, and the voltage is rectified and further increased, before arriving to the applicator, see Fig. 3. Finally,  $\bar{y}(t) = [IM; HV\_Actual]^T$  denote current and voltage measurements, respectively, which are fed back into the HVC. It is further noticeable that from a paint robot application point of view, it is given that  $HV\_SetPoint \in 0 \cup [3090], kV$ , that is, once the highvoltage is activated and turned on, it requires values larger than 30kV, and that the  $r(t) = HV\_SetPoint$ reference value does not change very often, and never faster than within 10 seconds from the previous change. These facts will be used subsequently in order to formally capture and verify some basic properties for HVC.

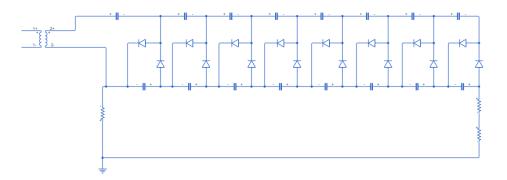

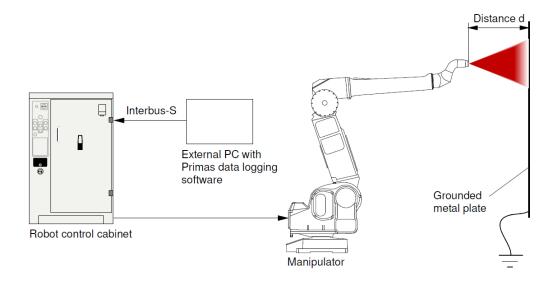

Following the line of thought in [14, 15], in order to distinguish and describe both the control software and physical hardware components of the HVC system, a faithful model of the PWM hardware is needed. The PWM hardware comprises the components inside the dashed blue box in Fig. 2, that is, the transformer, CW cascade block and resistors. Fig. 3 depicts the diodes, capacitors and resistors defining a CW cascade block as modelled in Simulink Simscape, which allows modelling of physical components and systems. It is noteworthy that by design, each section of the CW block will double the input voltage so that the output voltage of a CW cascade with N sections will equal  $2NV_{in}$ . The Simulink models used in this work are based on and extracted from experimental laboratory tests performed in [5, 6] on real ABB paint robots as depicted in Figs. 4 and 5. This serves as a back-drop and starting point for our work.

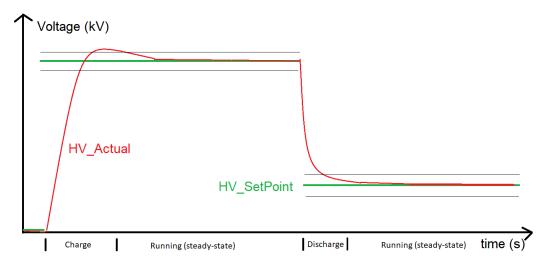

The paint robot HVC application has some further distinguishable structure and dynamics that will need to be considered and incorporated into our formal verification scheme. As detailed in [5, 6], the PWM hardware model and cascade controller are based on three distinct *modes* as graphically illustrated in Fig. 6:

Figure 3: The cascade modelled in Simulink with Simscape components, with the transformer, resistors and the Cockroft Walton voltage multiplier circuit.

Figure 4: Setup for experimental testing with paint using ABB robot. Photo courtesy ABB, from [5].

Figure 5: Schematic overview of the lab setup for testing ABB paint robot. Photo courtesy ABB, from [5].

- Charge: when a new external setpoint,  $HV\_SetPoint(t)$ , with higher value than the current one arrives and the PWM hardware is ramping up the control signal,  $u(t) = PWM\_Output(t)$ , in order to increase the value of  $HV\_Actual(t)$ .

- Running (steady-state): when HV\_Actual has converged to HV\_SetPoint and reached a steady state.

- **Discharge:** when the external *HV\_SetPoint* is set to a lower value and PWM hardware is discharging so that *HV\_Actual* converges to *HV\_SetPoint*.

Figure 6: The HVC hardware and controller has three distinct *modes*: Charge, Running (steady-state) and Discharge. The Integrated Painting System (IPS) parameters *RampLimit* and *TauPeriod* provide upper limits on the duration of the Charge and Discharge modes respectively.

It is further noticeable that by design [53], there are additional limits on peak deviation between  $HV\_Actual$  and  $HV\_SetPoint$  as well as the time duration of the Charge and Discharge modes. Namely, a

parameter RampLimit determines the maximum time in seconds that it will take to ramp up the high-voltage from minimum to maximum level, i.e., from 0 to 90 (kV). The default value of RampLimit is 2 seconds. Likewise, it is known that it will take TauPeriod seconds for  $HV\_Actual$  to reach a level of 30% above a new lower  $HV\_SetPoint$  value. The default value of TauPeriod is 3 seconds. Additionally, there are maximum allowed over and under voltage limits. As mentioned earlier, the HVC application, once activated and turned on, requires high-voltage values larger than 30kV, so that  $HV\_SetPoint \in 0 \cup [3090]kV$ . Consequently, the aforementioned limits are only specified at 30 and 90kV and over/under limits at other voltage levels can be calculated using simple linear interpolation between these values. All of these parameters are used for safety supervision purposes and are hence set in a conservative manner. In the next section, these parameters will be used to formulate and later formally verify the practical convergence property of the HVC controller to a new high-voltage setpoint.

## 3.1. Properties for Formal Verification

In this section, the set of four properties that are to be formally verified is presented. Recognising that the HVC has a rather generic form of a feedback controller, it is notable that most of the properties in this section are rather natural and generic properties to be fulfilled by any feedback controller tracking a setpoint reference.

Property **P1**. To start with, it is natural to require that the measured process value, which in the case of the HVC is dependent on time, t, and denoted  $y(t) = HV\_Actual(t)$ , should converge to the referenceor setpoint value,  $r(t) = HV\_SetPoint(t)$ . To formalize this, it is noted that both voltage signals are non-negative time-series and that convergence may be defined by setting

$$e(t) = |r(t) - y(t)| = |HV\_SetPoint(t) - HV\_Actual(t)|,$$

(1)

and equivalently considering (asymptotic) Lyapunov stability of the error term, e(t), to origin.

Taking the particular structure and dynamics of the HVC application as discussed previously into account, this setpoint convergence property can in practice be decomposed into considering a 10 second timeinterval directly after a new setpoint arrives, within which *practical convergence* of  $HV\_Actual$  to a narrow interval centered around the new external setpoint ( $HV\_SetPoint$ ) can be shown. To ease the notation and provide symmetry between the Charge/Discharge modes, let

$$\tau = \tau_0 + \max(RampLimit, TauPeriod), \tag{2}$$

where  $\tau_0$  denotes the time instance when a new setpoint arrives. Also conservatively, set the peak deviation from new  $HV\_SetPoint$  as 30% of the setpoint value. The width of this narrow interval, as well as schematic time changes and evolution of  $HV\_SetPoint$  and  $HV\_Actual$  are depicted in Fig. 6.

This system-level property involves both hardware and software components and can be formally specified as follows:

**P1:** Practical convergence of the actual system voltage, HV Actual, to the external setpoint, HV SetPoint:

$$\forall t \geq \tau \implies e(t) < 0.3 \times \max(HV \ SetPoint(t), 1).$$

Property P2-P3. To avoid residual effects and windup behaviours in the HVC, it is also reasonable to verify that both  $PWM\_Output$  and the software internal representation of  $HV\_SetPoint$ , denoted mSetPoint, are set to 0 whenever the 24V power signal, and thereby the HVC-module, is switched off. Here, mSetPoint is distinguished from  $HV\_SetPoint$  which is a software extrinsic signal set a priori by a human operator or application engineer.

These two properties can be formulated as follows:

**P2:** That *PWM\_Output* is set to 0 whenever the 24V power signal is off:

$$24V \quad Power = 0 \implies PWM \quad Output = 0$$

**P3:** That *mSetPoint* is set to 0 when the 24V power signal is switched off:

$$24V \quad Power = 0 \implies mSetPoint = 0$$

Property P4. Finally, in order to increase the confidence in the correctness of the model, it is customary to verify that the HVC state machine is not able to go into deadlock.

**P4:** That the HVC software is not able to go into deadlock.

These are the four properties that collectively need to be formally verified for the HVC application. System-level property **P1** is verified using our co-verification approach, which is the subject of Section 4, while the verification of properties **P2-P4**, that only concern the software, is discussed in Section 5. Next we present an overview of the overall behaviour of the HVC software.

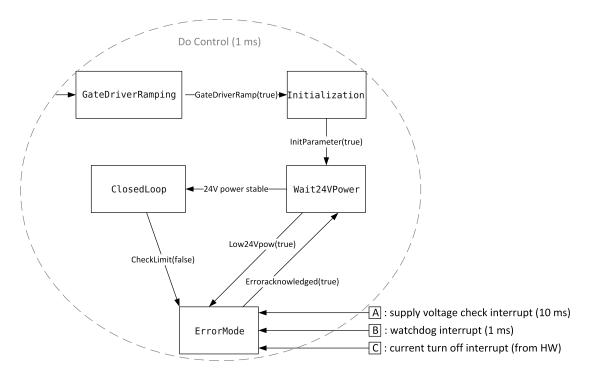

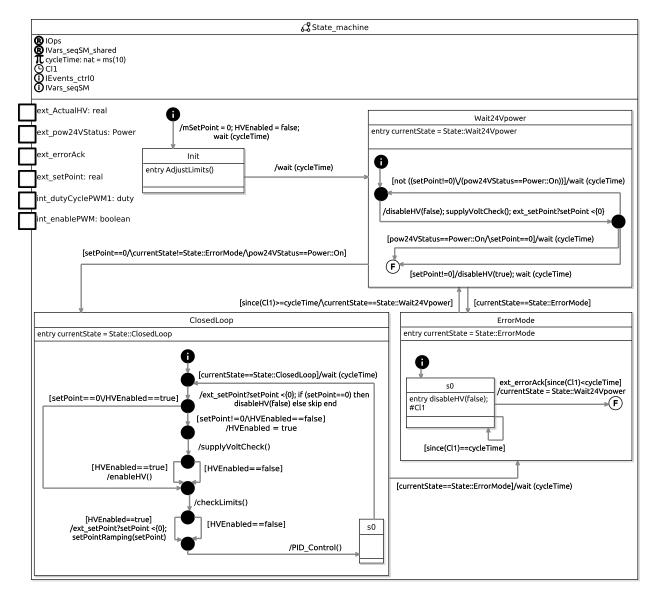

#### 3.2. Finite State Machine Overview

In order to perform model checking on the HVC, its functionalities were modelled as a finite state machine. This section presents the general finite state machine as depicted in Fig. 7. This high-level state machine was given by ABB and then further detailed and modelled in RoboTool. This is the topic of Section 4.2.2.

In the state GateDriverRamping, which is the state that the HVC first enters when it is switched on, the PWM duty-cycle is ramped up gradually to ensure stability and gradual increasing of current and voltage. Then, in the Initialization state, initial parameters are set, as well as upper and lower limits for the high-voltage.

After the GateDriverRamping and Initialization steps are successfully finished, the state machine enters the Wait24VPower state. When the HVC has 24V power switched on and is stable, the system enters the ClosedLoop state. This is the ideal state for operation, and is where the controller is regulating the voltage in relation to the setpoint. If the voltage breaches the upper or lower limits, the state machine moves from ClosedLoop to ErrorMode.

There is also a possibility to enter ErrorMode from the ClosedLoop and Wait24VPower states, if certain variables are set or any watchdogs or interrupts are triggered. For instance, an interrupt is triggered if the supply voltage is below a certain threshold, and another is triggered if  $HV\_Actual$  is above or below the upper and lower limits, respectively. Getting out of ErrorMode requires manual acknowledgement of the occurred errors.

## 4. Hardware/Software Co-Verification

To reason about system properties, such as Property P1, it is necessary to consider the behaviour of both software and hardware. We propose a novel approach, where properties are established by co-verification of models connected via platform mappings that relate the inputs and outputs of software and hardware, via sensors and actuators. Providing a crisp and systematic separation between hardware and software has some distinct advantages. To start with, with this approach, behavioural properties of individual models – that may be established using domain-specific tools – can be combined to support the verification of system properties. Also, our approach enables explicit recording and capturing of all dependencies and relations between hardware and software, which, when neglected, are implicitly assumed to be the identity mapping. Further, and as previously mentioned, the ongoing industrial trend is moving an increasing number of safety functions from physical hardware to software implementation. Still, the reliability, dependability and trust levels are very different between hardware and software components in an industrial robotic system. This framework hence sets the stage for more realistic and refined safety and risk handling procedures. Finally, the framework invites for combined approaches to modelling both discrete and continuous aspects in an integrated way while allowing the time-scale separation that typically exists between hardware and software components.

As an illustrative example, in our case study, the software is modelled in RoboChart, while the hardware is modelled in Simulink. RoboChart [10] is a domain-specific language for the model-based engineering of

Figure 7: Finite state diagram of the high-voltage Controller (HVC), showing its states and the conditions for transitioning between them. The ClosedLoop state is the ideal state for operation, and is where the controller is regulating the voltage in relation to the setpoint.

control software for robotics, that caters for timed and functional aspects. Its formal semantics is tailored for reasoning, namely using the CSP [54] model checker FDR [13]. However, it currently lacks facilities to specify the behaviour of the hardware. Simulink [12], on the other hand, is a *de facto* standard for control engineering, typically used for dynamic simulation in the industrial setting of the HVC [5, 6] system.

For modelling, we use Simulink and RoboTool [11, 9], that allows the graphical creation of RoboChart models, and for verification we use Simulink Design Verifier (SDV) [12] and FDR. System Property P1 is co-verified by model-checking, using the formal semantics of the control software, as calculated by RoboTool, and an abstract specification of the hardware behaviour, as established using SDV. These are formalised in *tock*-CSP [54, 55], the discrete-timed process algebraic semantics of RoboChart, for checking with FDR.

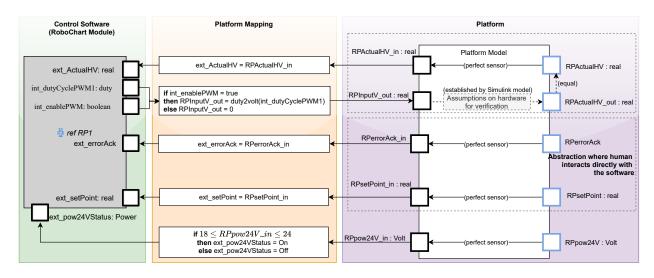

The complete system behaviour is considered at a suitable level of abstraction for verification by: (1) defining a platform mapping; (2) using a specification of the hardware that captures at an abstract level the relation between its inputs and outputs, as verified using SDV; (3) formalising these in *tock*-CSP. We depict the approach in Fig. 8 and explain it in detail in the next Section 4.1. In Section 4.2 we discuss the co-verification of system properties, modelling of the hardware and software, and the mechanisation in CSP of the overall framework. In Section 5 verification of properties of the software is also discussed.

#### 4.1. Framework overview

In our framework, the software and hardware models are coupled via interfaces that capture their inputs and outputs, with connections between models specified via platform mappings. On the left-hand side of Fig. 8 we consider the interface of the HVC control software, defined as a robotic platform (RP1) in RoboChart, that specifies the inputs and outputs as (possibly typed) events, indicated by solid boxes.

On the right-hand side we have a high-level description of the hardware platform, that captures its sensors and actuators. In our abstraction of the HVC platform, that comprises the cascade in Fig. 2, the hardware receives an input voltage, via RPInputV out, and produces a high-voltage via RPActualHV out.

Figure 8: Co-verification framework, with arrows indicating the direction of the information flow between inputs and outputs, of the software and hardware models. The platform mapping captures the relation between the software and hardware model on either side.

We also annotate important assumptions about the hardware that are of relevance for analysis: sensors are perfect, and, in particular, the voltage produced via RPActualHV\_out is assumed to be the same as that sensed via RPActualHV. The relation between RPInputV\_out and RPActualHV\_out is established by the Simulink model as detailed in Section 4.2.2, but abstracted for verification, as explained later in Section 4.2.4. The input signals RPerrorAck and RPsetPoint are an abstraction over the inputs available to a human operator, whose interaction with the software is realised via the platform.

The relation between the software and hardware model is specified by the platform mapping, as illustrated in the middle of Fig. 8. It records how the inputs and outputs of the software are connected to sensors and actuators of the hardware platform, as realised by low-level code and physical interfaces. The mappings for the software inputs ext\_ActualHV, ext\_errorAck and ext\_newSetPoint are trivial, as the software reads directly from these idealised sensors. The input ext\_pow24VStatus, of type Power, has the value On if the reading from the hardware, via RPpow24V\_in is between 18 and 24 Volts, and otherwise has the value Off.

The software outputs int\_dutyCyclePWM1 and int\_enablePWM are used to determine whether a voltage is produced via RPInputV\_out. If the value set via int\_enablePWM is true, then the value of RPInputV\_out is determined by the value of int\_dutyCyclePWM1, otherwise it is 0. This captures the fact that the PWM needs to be enabled in order to produce a voltage. Here, the function duty2volt maps a percentage, from 0 to 100% to the range of the analog 0 to 10 voltage signal as previously mentioned in Section 3.

More generally, when the connection between software and hardware is realised directly via reading and writing to registers of sensors and actuators, a platform mapping can be specified by a relation. As in the case of the input RPpow24V\_in, a voltage is related to a discrete set of values On and Off. On the other hand, if inputs of the software are interpreted as event-driven interrupts, a more appealing approach is to define when an event is available [15] using a predicate over the output of one or more sensors. Similarly, an input to an actuator may be constrained, for example, by a predicate over one or more software outputs.

# 4.2. System verification

Using the co-verification framework as illustrated in Fig. 8, in this section we address the formal verification of system Property **P1**. As described in Section 3.1, it requires practical convergence of the high-voltage (RPActualHV\_out) to the value of the setpoint as set by the user (RPsetPoint). Since the software is modelled in RoboChart, and the hardware in Simulink, our pragmatic verification strategy consists of: (1) capturing **P1** as a specification in *tock*-CSP; (2) showing practical convergence of the hardware output RPActualHV\_out in relation to its input RPInputV\_out using SDV; (3) casting the result obtained from

| Process                      | Description                                                                             |  |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|

| SKIP                         | Terminating process                                                                     |  |  |  |  |

| WAIT(d)                      | Delay: terminates exactly after d units of time have elapsed                            |  |  |  |  |

| STOP                         | Deadlock: no events are offered, but time can pass                                      |  |  |  |  |

| USTOP                        | Timelock: no events are offered and time cannot pass                                    |  |  |  |  |

| a -> P                       | Prefix operator: initially offers to engage in the event a while permitting any         |  |  |  |  |

|                              | amount of time to pass, and then behaves as $P$                                         |  |  |  |  |

| if g then P else Q           | Conditional: behaves as $P$ if the predicate $g$ is true, and otherwise as ${\tt Q}$    |  |  |  |  |

| P [] Q                       | External choice of $P$ or $Q$ made by the environment                                   |  |  |  |  |

| P;Q                          | Sequence: behaves as $P$ until it terminates successfully, and, then it behaves as $Q$  |  |  |  |  |

| P \ X                        | Hiding: behaves like P but with all communications in the set X hidden                  |  |  |  |  |

| P  \ X                       | Project: behaves like P but with all communications not in the set X hidden             |  |  |  |  |

| P     Q                      | Interleaving: P and Q run in parallel and do not interact with each other               |  |  |  |  |

| P [  X  ] Q                  | Generalised parallel: $P$ and $Q$ must synchronise on events that belong to the set $X$ |  |  |  |  |

| P[[ c <- d]]                 | Renaming: replaces uses of channel $c$ with channel $d$ in $P$                          |  |  |  |  |

| P /\ Q                       | Interrupt: behaves as $P$ until an event offered by $Q$ occurs, and then behaves as $Q$ |  |  |  |  |

| P [  X  > Q                  | Exception: behaves as $P$ until $P$ performs an event in $X$ , and, then behaves as $Q$ |  |  |  |  |

| TRUN(X)                      | Continuously offers the events in the set X to the environment, while time can pass     |  |  |  |  |

| <pre>timed_priority(P)</pre> | Maximal progress: behaves as P with internal behaviour given priority over tock,        |  |  |  |  |

|                              | so that internal behaviour takes no time                                                |  |  |  |  |

Table 1: *tock*-CSP operators as used in a **Timed** section, with basic processes at the top, followed by composite processes: P and Q are metavariables that stand for processes, a, c, and d for events, g for a condition, and X for a set of events.

SDV as a *tock*-CSP specification; (4) checking with FDR that, when combined with the semantics of the RoboChart model, via a mechanisation of the framework depicted in Fig. 8, **P1** is satisfied. That overall property **P1** holds is justified by the timed process algebraic semantics of RoboChart and the abstract specification (2-3) as established using SDV, and captured in CSP. A full account of the CSP specifications for all of the properties considered in this paper can be found online<sup>1</sup>.

*Formal Semantics.* The formalism that we use, *tock*-CSP, is a dialect of the process algebra CSP, where the event *tock* marks the passage of discrete time. As CSP adopts a reactive paradigm, interactions with the environment are specified using events, and that includes the passage of time in the case of *tock*-CSP. Importantly, it allows the specification of timed budgets and deadlines, and has a denotational semantics for refinement [55]. Relevant for our work, the model checker FDR has tailored support for *tock*-CSP.

In Table 1 we summarise the *tock*-CSP operators that we use in our work. To illustrate the notation we present a simple CSP specification of a one-place timed buffer in Listing 1 written in  $CSP_M$ , the machine-readable version of CSP accepted by FDR. The declaration on line 1 introduces a named type data whose values are defined by the set of integers between 0 and 2. Line 2 declares two typed **channels** named in and out, that can be used as event constructors using the dot notation, for example, in.0 and out.1. Related, the set of events generated by one or more event constructors can be specified as an enumerated set, so that, for example,  $\{|in|\}$  is equal to  $\{|in.0, in.1, in.2|\}$ , the set of all in events.

Processes defined within a **Timed** section<sup>2</sup> (lines 6-9) are interpreted to be timed: *tock* events are automatically added to allow time to pass when waiting for interactions with the environment, and the passage of time is uniform across interacting processes. The function OneStep, defined on line 4 to be 0 for every event in its domain (indicated by the underscore in its signature), is passed as a parameter (line 6) to the **Timed** section to ensure that no time is added implicitly after every synchronisation with the environment.

The behaviour of the timed buffer is that defined by the process Example (line 7) that behaves as TimedBuffer with timed\_priority applied, a function over processes, provided by FDR to calculate the

<sup>&</sup>lt;sup>1</sup>https://github.com/UoY-RoboStar/hvc-case-study

<sup>&</sup>lt;sup>2</sup>https://cocotec.io/fdr/manual/cspm/definitions.html#csp-timed-section

```

nametype data = {0..2}

channel in, out : data

OneStep(_) = 0

Timed(OneStep) {

Example = timed_priority(TimedBuffer)

TimedBuffer = in?x -> (TimedBuffer [] (WAIT(1) ; out!x -> TimedBuffer))

}

```

Listing 1: Example of a one-place buffer that is always prepared to receive a value, but which delays its output by one time unit.

```

timed csp SpecP1 csp-begin

channel e, RPsetPoint : core_real

Timed(OneStep) {

SpecP1 = timed_priority(Follow(s(3)))

Follow(d) = e?x \rightarrow (if x == 0)

then Follow(d)

else ((ADeadline({|e|},{|e.0|},d) ;

TRUN({|e.0|}))

/\ RPsetPoint?x -> Follow(d))

)

RPsetPoint?x -> Follow(d)

Allows time to advance by 'd' units while events from 'S' are performed until an event from 'S' that is in 'E' is performed.

ADeadline(S,E,d) = EndBy(TRUN(S),d) [|E|> SKIP

-- Built into RoboTool: deadline for 'P' to terminate within 'd' units.

EndBy(P,d) = P / (WAIT(d); USTOP)

}

csp-end

```

Listing 2: Specification for Property P1 defined within a RoboChart assertions' process block named SpecP1.

correct timed semantics [55]. TimedBuffer (line 8) initially offers to receive a data value via a prefixing on the channel in, and then offers an external choice ([]) to the environment between accepting a new value, via the recursion on TimedBuffer, or delaying the output of the current value, via prefixing on out after the sequential composition (;) with a delay of one time unit (WAIT(1)). We observe that an external choice is not resolved by the passage of time, but rather by synchronisation on events. Here, in?x is syntactic sugar for accepting events in.x where x ranges over the type data. The prefixing on out!x takes the value of x as introduced into context by the prefixing on in?x.

Specification. Following the description of **P1** in Section 3.1, here we construct a discrete version in *tock*-CSP, as shown in the RoboChart **timed csp** block named SpecP1 in Listing 2. It declares two **channels** (line 2), **e** and **RPsetPoint**, of type **core\_real**. The event **e** is used to model the absolute difference between ActualHV\_out and RPsetPoint, so that the specification can capture the relation between changes in **RPsetPoint** and the absolute difference.

The behaviour of SpecP1 is that of Follow, a process with a single parameter d, defined on lines 6-12 as an external choice ([]) over accepting events e or RPsetPoint, via prefixing (?x ->). Synchronisation on RPsetPoint, with any value, or e, with value 0, is followed by a recursion on Follow. Whenever the event e carries a value that is not 0 (lines 8-9), then Follow behaves as the process ADeadline({|e|},{|e.0|},d), that ensures an event e with a value of 0 can only be observed within d time units (instantiated as 3s for SpecP1), and afterwards behaves as TRUN({|e.0|}). This behaviour can be interrupted (/\ on line 9) at any time by a new RPsetPoint. We observe that for the purpose of model-checking the reals, modelled by the type core\_real, are instantiated in the discrete domain 0 to 2, so here we consider the difference e(t),

21

1 2

3 4 5

6

7

8

9

encoded via the event e, to be 0, without loss of generality.

The auxiliary process ADeadline(S, E, d), defined on line 16, takes three parameters, two sets of events, S and E, where S is expected to be a subset of E, and a natural number d. It continuously offers events in the set S, but time can only advance by up to d units, unless an event from the set E happens, in which case the process terminates. It is defined using the exception operator of CSP ([|E|>), where initially the behaviour is that of EndBy(TRUN(S), d), that continuously offers events in set S, and allows time to advance by up to d time units. Thus, within the exception, if TRUN(S) performs an event that is in E, then the process behaves as **SKIP**, that terminates immediately.

We observe that the auxiliary processes TRUN and EndBy are included with the RoboTool distribution for convenience. EndBy(P,d), reproduced on line 19, is a deadline over process P to terminate within d time units. It behaves as P, but because time is uniform in *tock*-CSP it requires the right-hand side process WAIT(d); USTOP to agree on the passage of time. That process, however, is only prepared to let d time units to pass before it timelocks, effectively imposing a deadline. Next, we focus on the hardware model.

#### 4.2.1. Hardware Modelling and Verification in Simulink Design Verifier (SDV)

Both the co-verification regime detailed in Section 4.1, as well as verification of the system-level properties, require a distinct and systematic separation between hardware and software components of the HVC system. Fig. 8 provides an overview of this separation and the steps toward implementing this have been set forward in the ingress of Section 4. To this end, the focus of this section is centered around hardware modeling, specification, abstraction and verification of hardware properties in SDV. All of these components are naturally combined in order to co-verify system-level properties.

Simulink is widely adopted as a tool for traditional, input-driven simulation, and the modelling in SDV is similar to regular modelling used for simulation [12]. SDV uses Prover Plug-In® products from Prover® Technology to do model-checking and prove the model properties [56]. It is built upon Gunnar Stålmarck's proof procedure, which uses tautology checks to prove that an assertion holds true in every possible interpretation [57]. In Property Proving mode, SDV offers three different proof strategies, Prove, FindViolation and ProveWithViolationDetection where the latter is merely a serial combination of the two first mentioned. In this work, both Prove and FindViolation have been used. Prove performs an unbounded property proof, while FindViolation searches for property violations within the number of steps specified by the Maximum violation steps option, which specifies the maximum number of steps that SDV searches for property violations. Thus, verification with increasingly large Maximum violation steps will help to increase confidence in the property.

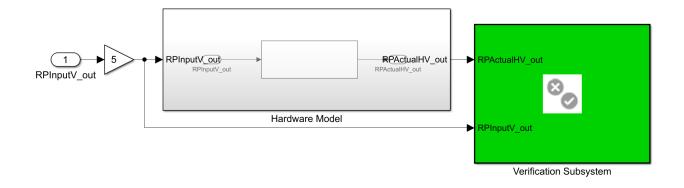

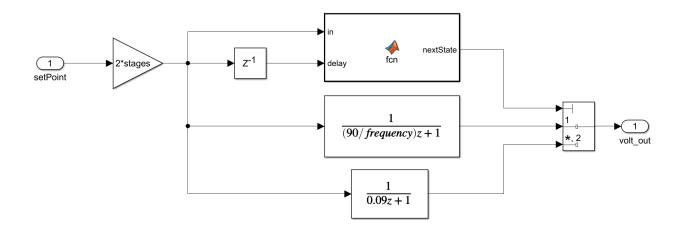

The Simulink Model. The hardware model in Simulink was created based on previous models found in [5, 6]. These models have been validated both theoretically and empirically by several lab experiments, and correspond well to the real-world system. In order to do formal verification with SDV however, the model had to be converted from continuous to discrete time, since SDV does not support continuous time. In this process, in addition to converting transfer functions specified in continuous time using Laplace transform (S-domain) to discrete time Z-domain, some of the Simulink blocks specific to continuous time were replaced with their discrete counterparts. Fig. 9 shows the overview of the hardware verification model in SDV where the input/output signals, *i.e.*, RPInputV\_out and RPActualHV\_out denote the same signals as previously introduced in Section 4.1 and Fig. 8. The mapping and transfer function between these two signals, and formal verification of certain hardware properties treated in this section, then correspond naturally to the extension and scope of the dashed grey box on the upper right side of Fig. 8.

It is noteworthy that, the input, RPInputV\_out, ranges over the discrete domain,  $\{0, 1, 2\}$ , and is multiplied by a constant factor 5 in Simulink, effectively corresponding to having the set of possible values of  $\{0, 5, 10\}$  volt being fed into the PWM hardware model. This means that duty2volt maps a percentage, from 0 to 100% to the entire range of the analogue [0 10] voltage signal as previously mentioned in Section 3. It also implies that the convergence results obtained in this section using  $\{0, 5, 10\}$  volt as input, will also be valid for the real PWM hardware system. This is because its input set, [0 10], is a superset of  $\{0, 5, 10\}$ .

The test data used to create the model was collected from structured experiments running at many different HV setpoints, frequencies, distances and number of stages in the CW-cascade, providing a rich

Figure 9: Overview of the hardware verification model. The grey box includes the modelling of the cascade, while the green box contains the property for verification.

data-set to represent how the actual hardware will behave in the real environment. As detailed in [5, 6] and depicted in Fig. 10, the Simulink model will, in addition to the ideal transfer function, have two additional terms describing the cascade loss and ripple effects. Using the Matlab System Identification Toolbox, state-space models and transfer-functions are fitted to the lab test data to provide the best description of the PWM hardware dynamics; both during the charge and discharge modes of operation. The resulting transfer functions and model components in continuous time can be seen in Fig. 10. Additionally, a Simulink model describing the bell-cup inside the applicator that will effect the electrical field at a plane at a given distance, d, from the paint robot, has been derived in [5] and used here.

Figure 10: Simulink model of the total CW-cascade hardware complementing the ideal model with loss and ripple terms [6].

In order to be able to formally verify the system-level property, **P1**, the mapping and relational properties between RPInputV\_out and RPActualHV\_out, effectively describing the hardware, is needed. This allows us to obtain a well-defined "closed circuit" mapping between all of the components in the co-verification framework of Fig. 8. To this end, the System Identification Toolbox was used to model the transfer function describing the relation between these two signals. This resulted in a standard, second order transfer function model:

$$G(s) = \frac{K_p}{(1+T_{p1}s)(1+T_{p2}s)},$$

(3)

having the following specific parameters

$$K_p = 1.1196$$

$T_{p1} = 0.087821$

$T_{p2} = 0.02042.$

Figure 11: Simulink model of the ideal cascade including the mode model selector and the two transfer functions describing the charging and discharging modes respectively [6].

This model was then analysed in Simulink with particular attention to time dynamics, stability and convergence properties as defined by, *e.g.*, rise and settling-time. Of particular interest in the following, is the settling time,  $t_s$ , which was found to be  $t_s = 0.3668s$ .

*Formal Verification of Hardware Properties.* Based on the developed Simulink model, next, we will be verifying a low-level property that will then be used in the co-verification scheme in order to verify Property **P1**.

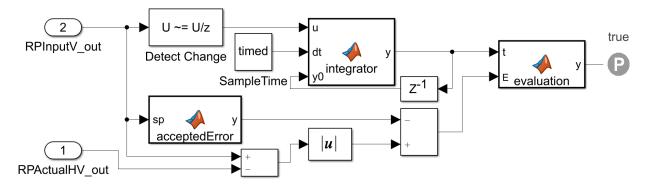

Referring back to the definition of Property P1, the error term Eq. (1) as well as the notion of *practical* convergence in Section 3.1, the following hardware property will be considered and verified in this section:

$\mathbf{P}_{\mathbf{HW}}$ : Practical convergence of actual hardware output voltage, RPActualHV\_out, to the hardware input signal, RPInputV\_out, within settling time,  $t_s$ :

$$\forall t \ge t_{sp} + t_s \implies E(t) = |\mathsf{RPInputV} \quad \mathsf{out}(t) - \mathsf{RPActualHV} \quad \mathsf{out}(t)| - 0.15 \times \max(\mathsf{RPInputV} \quad \mathsf{out}(t), 1) \le 0.$$

(4)

Here,  $t_{sp}$  denotes the time instance where an update to the input, RPInputV\_out, is received in PWM hardware. It is notable that while Property P1 is a system-level property, involving both software and hardware components, Property P<sub>HW</sub> as defined by Eq. (4) serves as a low-level hardware property. Another important distinction, stems from the difference in value between the settling time,  $t_s = 0.3668s$ , in Eq. (4) and  $\tau = 3s$  in Eq. (1) which implies that P<sub>HW</sub> incrementally contributes towards fulfilment of corresponding equations to verify the overall convergence Property P1. This fact also underlies and explains the difference in peak deviation limit (0.15 and 0.3 respectively) between the two properties.

The Simulink implementation to verify this property lies within the green Verification Subsystem in Fig. 9 and has been depicted in Fig. 12. The upper part containing the Detect Change block and an integrator function, works as a timer that is reset every time there is a change in RPInputV\_out. This in order to capture the  $t \ge t_{sp}+t_s$  constraint in Eq. (4). The lower part takes the absolute value of the error between RPInputV\_out and RPActualHV\_out and subtracts the accepted error, which is set to  $0.15 \times \max(\text{RPInputV}_out(t), 1)$ . Finally, the last function on the right, denoted evaluation, gives out false if Eq. (4) is not fulfilled at any time instance,  $t \ge t_{sp} + t_s$ . Otherwise it gives out true. This is verified with the proof assumption block, which shows if the property is fulfilled or violated.

After creating the model and the specification, the **Prove** strategy was used in order to verify the property. It was run both using MATLAB online and on a Windows laptop with Intel<sup>®</sup> Core<sup>©</sup> i5 CPU @ 2.71GHz. The online version and the desktop version were both used in order to run two verifications in parallel, to see if one would produce a result faster than the other. However, after running both continuously

Figure 12: SDV implementation of the PWM hardware convergence property,  $\mathbf{P}_{HW}$  as detailed in Eq. (4).

for 10 days without producing a result, the verification was manually terminated, with the assumption that the complexity had resulted in a state-space explosion that made Simulink unable to verify the specification. It was instead decided to gain increased confidence in the verification by using FindViolation with increasing Maximum violation steps. The results of the verification by using FindViolation can be seen in Table 2. The Maximum violation steps option was gradually increased, until reaching the maximum value of 2,147,483,647, which is the maximum value for data type int32. As seen in the table, SDV was able to prove that the property was valid within bound in all cases.

| Maximum violation steps | Fixed-step size<br>(fundamental sample time) | Result             | Elapsed time |

|-------------------------|----------------------------------------------|--------------------|--------------|

| 1,000                   | $1e^{-6}$                                    | Valid within bound | 0:47:49      |

| 1,000,000               | $1e^{-6}$                                    | Valid within bound | 0:46:44      |

| 1,000,000,000           | $1e^{-6}$                                    | Valid within bound | 0:47:15      |

| 2,147,483,647           | $1e^{-6}$                                    | Valid within bound | 0:47:15      |

Table 2: Results of the verification of the hardware, using FindViolation and different values for Maximum violation steps.

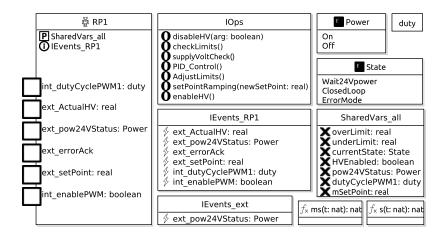

#### 4.2.2. Software Modelling in RoboChart

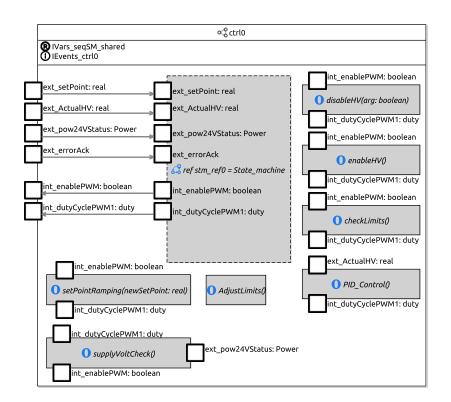

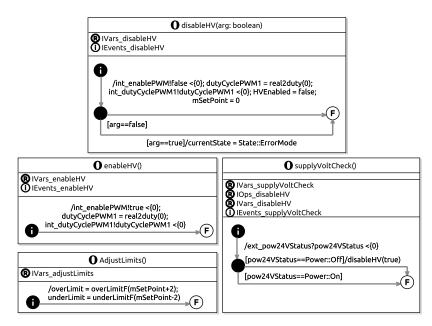

In this section, we present the RoboChart model of the software, that is a formalisation of the sketch previously shown in Fig. 7. The robotic platform (RP1) – a specification of the services available to the software in terms of variables, events and operations – is fully specified in Fig. 13. Its events are defined in the interface IEvents\_RP1. RP1 also provides the interface SharedVars\_all, that declares all of the shared variables that are used in the model. The interface IOps specifies the signature of the software operations that are used, and defined, in the RoboChart model. In addition to employing built-in data types, such as reals, naturals, and booleans, three data types are declared: the enumerated types Power and State, and the given type duty. Two functions ms and s are used to construct time units corresponding to milliseconds and seconds, respectively. RoboChart adopts the type system of Z [58, 59]. For a full account of the language and its formal semantics we refer the reader to [11, 16, 9]. Here, we describe the RoboChart constructs as we use them to model our example.

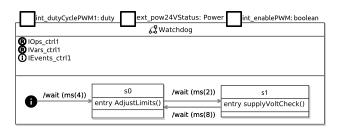

Module and Controllers. The top-level component of the software model is defined by the RoboChart module mod\_sys, shown in Fig. 14. It associates the robotic platform with four controllers (ctrl0-3), that capture specific behaviours. Controller ctrl0, shown in Fig. 15, contains the main State\_machine, that is a recast of that presented in Fig. 7, ctrl1 captures the behaviour of the watchdogs, and controllers ctrl2-3 are used to relay events. Controller ctrl2 relays the input event ext\_pow24VStatus from RP1 to controllers ctrl0-1, and ctrl3 relays the output events int\_dutyCyclePWM1 and int\_enablePWM from ctrl0 and ctrl1 to RP1, as RoboChart event connections are point-to-point. Due to their simple nature, the full definition of all

Figure 13: RoboChart model components: robotic platform ( $\mathbb{P}$  RP1), interfaces (named IOps, IEvents\_RP1, IEvents\_ext, and SharedVars\_all), enumerated (Power and State) and given (duty) data types.  $\frac{4}{7}$  is an event, X is a variable, and  $\mathbf{0}$  is associated with an operation.  $\mathbb{P}$  is used to record that an interface is provided, while  $\mathbb{O}$  is a used interface.

Figure 14: RoboChart module mod\_sys defining the connections between controllers and the robotic platform. Controller ctrl0 contains the main State\_machine, a recast in RoboChart of the state machine presented in Fig. 7. The watchdogs have been combined into one state machine, defined inside controller ctrl1. Controller ctrl2 relays the event ext\_pow24VStatus to controllers ctrl0 and ctrl1, while controller ctrl3 is used for relaying the events int\_enablePWM and int\_dutyCyclePWM1 to RP1.

controllers is deferred to an on-line report<sup>3</sup>. In RoboChart, connections with the platform are always asynchronous, indicated by the keyword async, as interactions with the platform cannot be refused, only ignored [10, p.3110]. The connections between all controllers ctrl0-3, however, are set as synchronous.

State Machine. The core behaviour of the HVC controller is captured by the State\_machine in Fig. 16. In RoboChart, state machines are self-contained by explicitly stating the required (O) variables and operations, and the used (O) events. In this case, State\_machine requires the software operations declared in IOps, and the shared variables in IVars\_seqSM\_shared. It also declares: local variables via the interface IVars\_seqSM, a constant cycleTime with a default value of 10 milliseconds, and a clock (O) Cl1. It uses the events of interface IEvents\_ctrl0, that are also explicitly listed on the left-hand side of Fig. 16.

<sup>&</sup>lt;sup>3</sup>https://robostar.cs.york.ac.uk/case\_studies/hvc/

Figure 15: Controller ctrl0, showing its inputs and output connections to Sate machine, and references of operations.

The execution flow of State\_machine starts at the initial junction, followed by a transition whose action, specified after the dash (/), initializes the value of the variables mSetPoint and HVEnabled, by assigning 0 and false in sequence (;), respectively. It then waits for cycleTime units before entering state lnit. This initial delay is a simplification of the GateDriverRamping behaviour depicted in Fig. 7, which does not concern the properties of interest for verification. In state lnit there is an entry action that calls the software operation AdjustLimits which calculates the value of variables overLimit and underLimit and is defined by a state machine as shown in Fig. 17. The required variables of AdjustLimits, as listed in interface IVars\_adjustLimits, are provided by State machine in the context of the call to AdjustLimits, effectively sharing the state.

After the initialization is complete, the execution proceeds to the composite state Wait24Vpower on the next cycle. Its entry action explicitly records that the state has been entered by setting the variable currentState. The transition to ClosedLoop is only enabled when the current value of setPoint is 0, the 24V power is stable (pow24VStatus==Power::On), and the ErrorMode is not activated, as indicated by the transition's guard. The body of Wait24Vpower monitors the relevant inputs periodically as part of the cycle of transitions between the junctions. Firstly, the operations disableHV and supplyVoltCheck, as defined in Fig. 17, are called. disableHV disables the high-voltage, while supplyVoltCheck checks the input ext\_pow24VStatus and updates the value of the variable pow24VStatus. Secondly, the value of the variable setPoint is also updated via a reading (ext\_setPoint) through event ext\_setPoint, with a deadline (<{0}) of zero time units. In RoboChart budgets and deadlines must be specified explicitly, and so here the deadline indicates that the reading takes a negligible amount of time.

The critical phase of HVC operation is captured in state ClosedLoop, that controls the PWM. Initially the user-defined setpoint, ext\_SetPoint, is read into the variable setPoint. If the value is zero, then disableHV is called to ensure that the high-voltage is disabled. Afterwards, if the value is non-zero and the high-voltage has not been enabled yet (HVEnabled==false), HVEnabled is set to true, the supply voltage is checked by calling supplyVoltCheck(), and the high-voltage is enabled by calling enableHV. While the high-voltage is enabled, the internal setpoint (recorded in variable mSetPoint) is adjusted by calling setPointRamping(setPoint). The

Figure 16: Main State\_machine corresponding to that of Fig. 7 recast in RoboChart.

Figure 17: Software operations modelled in RoboChart with their behaviour defined by state machines: disableHV disables the high-voltage by writing false to int\_enablePWM and setting the duty cycle to zero via int\_dutyCyclePWM1; enableHV enables the high-voltage; AdjustLimits calculates voltage limits, overLimit and underLimit, based on the current value of mSetPoint; and supplyVoltCheck checks whether the 24V power is stable via the input ext pow24VStatus, and if unstable calls disableHV.

Figure 18: Watchdog state machine. Initially there is a delay of 4 milliseconds before engaging in a cyclic behaviour. First AdjustLimits is called, and after 2 milliseconds supplyVoltCheck is called, with same behaviour repeated after a delay of a further 8 milliseconds. The call to supplyVoltCheck can disable the high-voltage if the 24V power is not stable, as shown in Fig. 17.

PWM duty-cycle is adjusted by PID\_Control that outputs a percentage via int\_dutyCyclePWM1, according to the difference between mSetPoint and ActualHV, the measured high-voltage via the input ext\_ActualHV. In state s0 of ClosedLoop, the flow of execution may be interrupted by transitioning to ErrorMode when currentState is set to State::ErrorMode. The error can be acknowledged via the event ext\_errorAck within the current cycleTime, after which there is a transition to Wait24Vpower.

The variable currentState may be set to State::ErrorMode by calling disableHV(true), either while in Wait24Vpower, or from within operations checkLimits or supplyVoltCheck, that checks whether the input 24V power is stable. The latter is called regularly in states ClosedLoop and Wait24Vpower of State\_machine, and also by the watchdog, which, as will be explained next, is modelled in another state machine.

*Watchdog.* The watchdog, shown in Fig. 18, executes, over time, in alternation with the main State\_machine, that executes on a 10 millisecond cycle, as specified by the constant cycleTime. Therefore, the watchdog's behaviour is initially delayed by 4 milliseconds. In state s0 there is a call to AdjustLimits(), and 2 milliseconds later, the operation supplyVoltCheck() is called. We observe that the transition between s1 and s0 takes 8 milliseconds, and it is during this time that State machine actually executes its cyclic behaviour.

```

timed csp HVC_Platform csp-begin

-- Data type used to characterise input RPpow24V

nametype Power_Voltage = {0,24}

channel RPActualHV_out : core_real

'Actuator' output

- - -

channel RPInputV_out

: core_real

- -

Output from software via mapping

channel RPActualHV, RPActualHV_in

Sensor input and platform mapping

: core real

: Power_Voltage

channel RPpow24V, RPpow24V_in

Sensor input and platform mapping

- -

channel RPsetPoint_in : core_real

- -

Sensor platform mapping

channel RPerrorAck, RPerrorAck_in

-- Untyped input and platform mapping

channel get_HV, set_HV, change : core_real

-- Used for abstraction of the hardware

Timed(OneStep) {

HVC_Platform = timed_priority((HV(0)[[ get_HV <- RPActualHV_out ]]

[| {|set_HV|} |]

HVC_Hardware)\{|set_HV|}

)

HV(x) = set_HV?nv \rightarrow HV(nv) [] get_HV!x \rightarrow HV(x)

HVC_Hardware = (Detector [| {| change, get_HV |} |] StatefulEvolution)\{|change, get_HV|}

Detector = RPInputV_out?nv -> get_HV?x -> (if nv != x

then (change!nv -> Detector)

else Detector)

StatefulEvolution = (Evolution [| {| change |} |] HV(0)[[ set_HV <- change ]])</pre>

Evolution = change?x -> ((WAIT(ms(370)); set_HV!x -> Evolution) [] Evolution)

csp-end

```

Listing 3: Mechanisation of the HVC\_Platform.

#### 4.2.3. Framework Mechanisation

Having developed models of the software and hardware, in this section we mechanise the co-verification framework outlined in Fig. 8 with the aim of verifying system Property **P1**. We start by defining a CSP process that captures Property **P<sub>HW</sub>**. This is followed by the complete mechanisation of the platform and its mapping, and the composition with the semantics of the RoboChart model, as calculated by RoboTool.

*Platform.* The hardware platform is specified within the **csp** block named HVC\_Platform, shown in Listing 3. It defines, first of all, the CSP<sub>M</sub> events of the sensors and actuators (lines 4-9), following the naming conventions of Fig. 8. The process HVC\_Platform is a discrete, and reactive, model of the hardware, constructed from the Property  $P_{HW}$  established in Section 4.2.1. It is defined as a parallel composition ([| |] on lines 14-16), synchronising on event set\_HV, of HV(0), that models the current value of the high-voltage, and HVC\_Hardware, that captures how the value of RPActualHV\_out may change over time in response to changes in RPInputV\_out. The process HV(x), defined on line 19, offers the event set\_HV to change the value, and the event get\_HV to query the current value x. It is specialised on line 14 as HV(x)[[ get\_HV <- RPActualHV\_out ]] by renaming the event get\_HV to RPActualHV\_out. The event set\_HV is hidden (\), as it is an artefact of the CSP model.

The evolution of the value available via RPActualHV\_out is modelled by the process HVC\_Hardware. It is defined on line 21 as the parallel composition of the process Detector, synchronising on the events change and get\_HV, and the process StatefulEvolution. The latter models how changes to the voltage evolve over time, while Detector, named analogously to the SDV block in Fig. 12, models how an input via RPInputV\_out may affect the behaviour. First it offers to receive a new value nv via RPInputV\_out, and then synchronises with StatefulEvolution on get\_HV to query the current value x being targeted. If the value is different, it synchronises on change with value nv, otherwise it behaves as Detector.

The core of the hardware property  $\mathbf{P}_{\mathbf{HW}}$  is abstractly captured by the process StatefulEvolution.

1

3 4 It is defined on line 27 as the parallel composition of Evolution, synchronising on event change, with HV (0) where the channel set\_HV is renamed to change. Evolution accepts a change event at anytime, and afterwards waits 370 milliseconds, a conservative natural approximation of the settling time of the Simulink model of the hardware, before synchronising on set\_HV, which is used to update the high-voltage, whose value is available via RPActualHV\_out, as modelled by the process HV(0) in HVC\_Platform. Thus, a change via RPInpuV\_out leads to a change in the value available via RPActualHV\_out over time, mirroring property  $P_{HW}$  as established in Section 4.2.1. Next, we describe the mechanisation of the platform mapping.

-- Function that maps the duty cycle percentage to the value expected by RPInputV\_out.

```

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

```

timed csp PlatformMapping csp-begin

```

duty2volt(x) = if member(x, \{0...19\}) then 0

else (if member(x, {20..60}) then 1

else (if member(x, {61..100}) then 2 else 0))

Timed(OneStep) {

PlatformMapping = timed_priority((RPInputV_out!0 -> PWM_Map(false)) ||| Pow24_Map(true))

- Platform mapping of duty cycle and PWM to RPInputV_out.

PWM_Map(pwm) =

mod_sys::int_enablePWM.out?x ->

((if x == false then RPInputV_out!0 -> SKIP else SKIP) ; PWM_Map(x))

[]

mod_sys::int_dutyCyclePWM1.out?x ->

((if pwm == true then RPInputV_out!duty2volt(x) -> SKIP else SKIP); PWM_Map(pwm))

-- Platform mapping from RPpow24V_in to ext_pow24VStatus.

Pow24_Map(pwr)

RPpow24V_in?x: \{x \mid x < -Power_Voltage, (x <= 24 and x >= 18)\} -> Pow24_Map(true)

\hat{RP}pow24V_in?x:{x | x <- Power_Voltage, (not (x <= 24 and x >= 18))} -> Pow24_Map(false)

[]

(if pwr==true

then mod_sys::ext_pow24VStatus.in!Power_On -> Pow24_Map(pwr)

else mod_sys::ext_pow24VStatus.in!Power_Off -> Pow24_Map(pwr))

csp-end

```

Listing 4: Mechanisation of the Platform Mapping.

*Platform Mapping.* The process PlatformMapping, defined on line 7 of the csp block in Listing 4, captures the non-trivial mapping between int\_dutyCyclePWM1, int\_enablePWM, and RPInputV\_out, and between RPpow24V\_in and ext\_pow24VStatus. It is an interleaving (|||) of two processes, Pow24V\_Map, that models the mapping between RPpow24V\_in and the software input ext\_extPow24VStatus, and the prefixing on RPInputV\_out with value 0 followed by the behaviour of PWM\_Map. Here the prefixing initializes the hardware with value zero. PWM\_Map, defined on lines 10-15, models the mapping between the outputs int\_dutyCyclePWM1 and int\_enablePWM, and the input to the platform RPInputV\_out.

PWM\_Map is parametrised to keep track of whether the PWM has been turned on or off. The first process in the external choice (lines 11-12) allows this value to be toggled depending on whether int\_enablePWM.out is received with value false, in which case the value zero is passed to the platform via RPInputV\_out, and otherwise there is a recursion on PWM\_Map(x) with the updated value of x. In the second process (lines 14-15), values received via int\_dutyCyclePWM1.out are passed to the platform via RPInputV\_out, mapped via the function duty2volt, if the value of pwm is currently true. This function, defined on lines 3-5, maps a percentage to a voltage, which, as previously discussed in Section 4.1, encodes three possible values.

The CSP process Pow24\_Map is defined analogously on lines 18-25 to model the mapping between the sensor of the 24V voltage, and the input ext\_pow24VStatus of the software, whereby a value between 18 and 24 is considered as On and otherwise as Off. The value that x can take on the prefixings on the channel RPpow24V\_in, on lines 19 and 21, is constrained using set comprehensions. This concludes the non-trivial mappings, which are used in the definition of the overall system next.

```

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

```

1

```

timed csp MappedSystem csp-begin

Timed(OneStep) {

-- Defined over the semantics of the RoboChart module 'mod_sys' calculated by RoboTool.

Software = mod_sys::0_(0,ms(10),1) [[ mod_sys::ext_ActualHV.in <- RPActualHV_in,

mod_sys::ext_errorAck.in <- RPerrorAck_in,</pre>

mod_sys::ext_setPoint.in <- RPsetPoint_in ]]</pre>

Software_PMap =

(Software

[|{|mod_sys::int_enablePWM.out,

mod_sys::int_dutyCyclePWM1.out,

mod_sys::ext_pow24VStatus|}|]

PlatformMapping)

\{|mod_sys::int_enablePWM.out,mod_sys::int_dutyCyclePWM1.out,mod_sys::ext_pow24VStatus|}

MappedSoftware = Software_PMap[[ RPActualHV_in <- RPActualHV,</pre>

RPerrorAck_in <- RPerrorAck,

RPpow24V_in

<- RPpow24V,

RPsetPoint_in <- RPsetPoint ]]</pre>

MappedSystem = timed_priority(MappedSoftware

RPActualHV_out <- RPActualHV]])</pre>

\{|RPInputV_out,RPActualHV|})

}

csp-end

```

Listing 5: Complete mechanisation of the Platform Mapping.

Mapped System. The complete system, as envisioned in Fig. 8 is modelled by the process MappedSystem within the csp block of Listing 5. It is defined on lines 20-24 as the parallel composition of MappedSoftware and HVC\_Platform, defined in Listing 3, synchronising on the events RPInputV\_out and RPActualHV. Here HVC\_Platform is relationally renamed [54, p. 105], so that the event RPActualHV\_out is both an output of the platform and also a sensor input, with the same value, via RPActualHV, as depicted in Fig. 8. The hiding on RPInputV\_out and RPActualHV completes the abstraction.

The process MappedSoftware, defined on lines 15-18, captures the connections between the composition of the platform mapping and the software, as established by Software\_PMap, and the platform, by renaming the events of the former to the latter. The sensors of the platform, in particular, are assumed to be perfect, and so in this abstraction the functional renaming is a record of their ideal functional behaviour.

Sofware\_PMap, defined on lines 7-13, captures the composition of the RoboChart CSP semantics, and the PlatformMapping, as defined earlier in Listing 4. It is a parallel composition of the processes Software and PlatformMapping, synchronising on int\_enablePWM.out, int\_dutyCyclePWM1, and ext\_pow24VStatus, corresponding to events of the RoboChart model. The process Software, which explicitly instantiates the RoboChart model semantics, is defined analogously to MappedSoftware, whereby the trivial mappings are captured via renaming. The hiding on line 13 completes the abstraction.

The process  $mod_sys::0_{(0,ms(10),1)}$ , used on line 4, is an explicit instantiation of the CSP<sub>M</sub> semantics of  $mod_sys$ , automatically calculated by RoboTool, where 0 is a default identifier, ms(10) is the value of constant cycleTime of State\_machine, and 1 the value of constant rampStep of operation setPointRamping. Events in the CSP semantics of RoboChart are named according to the model hierarchy, where :: is a delimiter, and have a parameter in or out to indicate whether an event is an input or output.

# 4.2.4. Formal Verification of System-level Property P1

With the framework outlined in Fig. 8 mechanised in CSP, in this section we address the verification of Property **P1**. Its specification in CSP, described in Section 4.1, is reproduced in Listing 6 for convenience. Verification of Property **P1** is stated as a refinement **assertion P1 in the traces model** of CSP (line 15), that ensures safety [54, p.36]. That is, an implementation P **refines Spec**, if, and only if, every behaviour of the implementation is a behaviour permitted by the specification. While RoboChart **assertions** are

```

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

```

Listing 6: Recall of SpecP1 as previously defined in Listing 2 and the RoboChart assertion for verification.

translated by RoboTool into CSP<sub>M</sub> refinement assertions, they can also directly reference elements of the RoboChart model to facilitate the checking of basic properties, such as deadlock freedom and termination [10, p. 3129]. For assertion P1, SpecP1 is the specification and ImplP1 is the implementation. As previously discussed in Section 4.1, SpecP1 is stated in terms of a new event e, that is not part of Fig. 8 but useful to specify Property P1 in terms of the absolute difference between the value of output RPActualHV\_out and input RPsetPoint. To facilitate verification, process ImplP1, is defined next to relate events e and RPActualHV\_out, and RPsetPoint, based on the process MappedSystem, previously defined in Listing 5.

System Interface for Verification of P1. We observe that in SpecP1, the event RPsetPoint is used as an interrupt, which emerges naturally in the reactive CSP setting. However, the event RPsetPoint as used so far in the definition of MappedSystem models readings of a sensor, that can be performed periodically despite no change in the actual value. Therefore, to relate SpecP1 and ImplP1, in Listing 7 we define a suitable mapping for the RPsetPoint event. We also capture the relationship between the event e and the current value of both the setpoint and the actual high-voltage, as required for the comparison with SpecP1.