Received 27 October 2023, accepted 21 November 2023, date of publication 23 November 2023, date of current version 29 November 2023.

Digital Object Identifier 10.1109/ACCESS.2023.3336567

## **RESEARCH ARTICLE**

# Integrated Multiport DC-DC and Multilevel Converters for Multiple Renewable Energy Source Integration

## IMMANUEL N. JIYA<sup>®1</sup>, (Member, IEEE), AHMED SALEM<sup>®1</sup>, (Associate Member, IEEE), HUYNH VAN KHANG<sup>®1</sup>, AND RAIMONDAS POMARNACKI<sup>®2</sup>

<sup>1</sup>Faculty of Engineering and Science, University of Agder, 4879 Grimstad, Norway

<sup>2</sup>Faculty of Electronics, Vilnius Gediminas Technical University, 10105 Vilnius, Lithuania

Corresponding author: Immanuel N. Jiya (immanueljiya@ieee.org)

This work was supported in part by the Research Council of Norway through the Integrated Renewable Resources and Storage: Operation and Management under Project 285545; in part by the University of Agder, Norway, under Project 63828; in part by the Project "Industrial Internet Methods for Electrical Energy Conversion Systems Monitoring and Diagnostics"; in part by Iceland, Liechtenstein, and Norway, through European Economic Area (EEA) grants under Grant 993000; and in part by the Project Contract with the Research Council of Lithuania (LMTLT) under Grant S-BMT-21-5 (LT08-2-LMT-K-01-040).

**ABSTRACT** This research introduces an innovative converter system which has been developed to seamlessly incorporate multiple sources of renewable energy into both DC and AC grids. The integration of multiple energy sources is made possible through the utilization of a unique converter system that combines a multiport DC converter topology with a multilevel inverter topology, while maintaining a low component count and hence increased overall power density and efficiency for the proposed converter system. Unlike previous literature, where each energy source needs a separate DC converter and a two-level converter is used for DC to AC conversion, this converter system features buck-boost operation, superior power quality characteristics, and fewer components. The system suggests the implementation of a DC link voltage balancing technique that relies on an auxiliary circuit to achieve equilibrium in the voltage on the DC link, as a possible substitute to the more complicated control-based balancing scheme. The operational integrity of the converter system is assessed through rigorous numerical simulations and experimentally validated using OPAL-RT's OP5700 hardware-in-the-loop (HIL) implementation platform as well as an in-house experimental test setup.

**INDEX TERMS** DC-DC converter, dc link capacitor balancing, multiport converter, multilevel inverter.

#### I. INTRODUCTION

Lately, there has been a rising awareness regarding the finite nature of fossil energy sources and the harmful environmental effects linked with their utilization in response to the escalating global energy requirements and market conditions. Consequently, a strong focus has been exploring sustainable energy options [1], [2], [3]. Fuel cells, wind turbines, and photovoltaic (PV) systems have demonstrated their potential as viable options for delivering environmentally-friendly solutions [4], [5]. The rising acceptance and integration of

The associate editor coordinating the review of this manuscript and approving it for publication was Inam Nutkani<sup>D</sup>.

renewable energy sources (RESs) are catalysing an important transformation in the landscape of electrical energy generation and utilization. This transition entails a fundamental shift from traditional centralized generation systems to more decentralized and distributed models [6], [7], [8], [9]. Future power systems are expected to rely heavily on distributed generation systems, which are primarily based on DC microgrids. DC microgrids have several advantages over AC microgrids, like the lack of issues with reactive power and synchronization. As a result, they are considered the backbone of future power systems [10], [11]. Nonetheless, AC power systems are widely prevalent in many traditional power systems, particularly in developing countries [12], [13]. Therefore, it remains crucial to convert power generated from renewable energy sources (RESs) from DC to AC [14].

Multilevel inverters (MLIs) have been gaining popularity as an efficient and effective solution for achieving high power DC to AC power conversion [15], [16], [17]. These inverters offer compelling advantages, for example, reduced total harmonic distortion (THD), minimal switching losses, negligible common-mode voltage (CMV), decreased compact filter components, electromagnetic interference, and enhanced thermal management capabilities, among various other benefits [18]. Compared to traditional two-level inverters, MLIs offer significant advantages, motivating researchers to develop new MLI topologies. Although numerous studies have proposed novel MLI topologies [19], [20], [21], conditioning the inputs of MLIs has remained challenging. This is due to the complex controllers required to maintain the desired output waveform, and the high voltage and current handling capabilities needed. Many current topologies operate under the assumption of constant DC inputs, which, while theoretically ideal, proves impractical in real-world scenarios due to the varying output voltages exhibited by most renewable energy sources (RESs) during their operation [22]. However, these challenges can be addressed using DC-DC converters [23], [24]. DC-DC converters can be used to condition the input voltage source for MLIs by stepping up or down the voltage to the required level [25]. This can be particularly useful when the input voltage source is not at the desired level, such as in RES applications where the input voltage from solar panels or wind turbines can vary [26].

Various attempts have been made to address the challenge of integrating RESs into the power grid, including proposing MLIs that can precondition the outputs of RESs before the conversion to AC takes place [27], [28], [29], [30], [31]. Nevertheless, the MLI configurations suggested in these studies have certain drawbacks. For example, these configurations may be limited to a single RES and can solely boost input voltage. To address these constraints, an alternative MLI design, as proposed in [31], integrates two RESs by employing two DC-DC converters connected in cascade configuration prior to the MLI stage. This integration allows for buck-boost functionality and facilitates the utilization of multiple inputs. However, this arrangement is not without its drawbacks, including a higher number of components, increased power losses, increased system costs, reduced power density, and efficiency.

Furthermore, other attempts were made to propose DC to AC converters comprising of integrated MLIs and DC-DC converters for RES integration in [32], [33], [34], [35], and [36]. However, these approaches also suffer from several limitations, such as the limitation on the number of RES inputs, number of phases and levels and the need for transformers for isolation, which result in bulky designs. More specifically, a family of multi-port modular multilevel converters is introduced in [35], interfacing one AC port with two DC ports with the help of low-frequency transformers. The reported topologies generate high voltage levels using either full-bridge or

half-bridge cells. Modularity and wide applicability are their main features, besides the limitless reachable voltage level counts. However, they face challenges due to the large number of required capacitors and switches, influencing the reliability and complexity of the conversion system, in addition to the well-known related drawbacks of using transformers, including size and cost. On the other hand, the authors in [36] proposed a transformerless three-port bidirectional converter structured by connecting a DC-DC buck-boost stage with a Ttype three-level inverter. The suggested converter eliminates the drawbacks associated with using transformers. However, it loses the modularity feature, restricting its suitability to low- and medium-voltage applications.

Moreover, integrating multiple RESs introduces the challenge of balancing the voltage across the DC link capacitors in MLIs. In certain cases, MLIs require multiple DC link capacitors connected in series to evenly distribute the DC link voltage among them. This is necessary to ensure proper operation and prevent voltage imbalances [22]. Hence, achieving voltage balance across these capacitors is crucial to preserve the integrity of output waveforms and ensure optimal power quality. However, attaining this balance entails the implementation of a sophisticated control system that can effectively regulate the voltage distribution among the capacitors [37]. This creates a unique opportunity to fill the gap by applying multiport converters in the integration of RESs to AC grid through MLIs, to achieve attractive features of low component count, high efficiency, low THD and higher power density.

The research presented in this paper introduces an innovative approach to tackle the mentioned challenges in RES integration. It involves the utilization of a multiport DC converter (MDC) as a means to integrate the RESs, resulting in reduced component count during the preprocessing stage. Consequently, this approach offers several benefits, including decreased costs, lower power losses, improved efficiency, and increased power density. Additionally, the research proposes the implementation of an auxiliary circuit to achieve a simplified DC link capacitor voltage balancing method, as opposed to the previously suggested control-based technique. The proposed configuration offers versatile capabilities, including buck-boost operation, as well as the ability to facilitate individual and simultaneous power transfer from multiple RESs. This flexibility allows for efficient energy management and optimized utilization of the available renewable energy sources. More specifically, the proposed converter system has the following novel features:

- 1) The number of input sources (RESs) can be arbitrarily increased.

- 2) It can transmit power from the inputs (RESs) to the DC and AC buses independently and simultaneously.

- 3) It can perform unidirectional buck and boost operations with a high voltage gain.

- When an extra input is introduced, only one additional reverse blocking switch is needed to increase the number of inputs.

5) The DC converter section simply needs a single input single output (SISO) controller, such as the common double loop PI controller, and has a straightforward control strategy as detailed and proposed in [38].

Within this framework, the new converter system was analyzed for three input sources with equal and different input voltage levels, put through extensive simulations, and experimentally verified. Rigorous numerical verification and validation is performed, using a state-of-the-art hardwarein-the-loop (HIL) device to assess the performance and operation of the converter system. This advanced testing methodology ensures that the converter system operates reliably and accurately under various operating conditions, providing confidence in its functionality and effectiveness. The initial idea of the integrated converter system proposed in this work has been presented in [39]. In this paper, the detailed analysis and features are numerically verified, and results from experimental validation using the HIL test rig are presented. HIL verification has been proved to accurately and sufficiently prove the operation of power converters [40], [41], [42] and, as such is implemented in the verification of the proposed converter system. Other key features of the proposed integrated converters have been vigorously addressed in [22] and [42], the individual converters from which the integrated converter is derived. These features include efficiency, dynamic response to disturbances, component selection, and voltage and current stress. Since they have been sufficiently addressed, they are not included in this paper.

#### **II. PROPOSED INTEGRATED CONVERTERS**

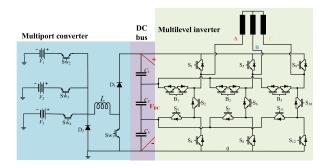

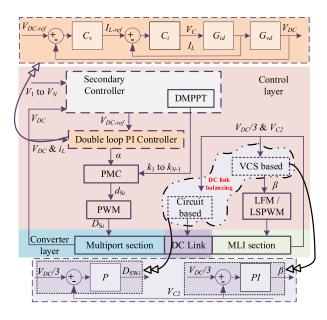

Figure 1 illustrates the combined multiport DC and multilevel converter system, which incorporates a new multiport DC-DC converter (synthesized from the converter in [42]) highlighted in blue color. The system also features a DC bus output colored in purple and incorporates the multilevel inverter portion colored in green, previously introduced in [22], responsible for generating the AC output. The proposed configuration provides a high degree of flexibility, allowing for the seamless integration of diverse RESs with varying voltage levels into both the DC and AC links. The system enables independent or simultaneous connection of these energy sources, facilitating efficient power flow and utilization in a versatile manner.

#### A. MULTIPORT DC CONVERTER TOPOLOGY

The region highlighted in blue in Figure 1 showcases the proposed novel topology of a unidirectional multiport DC to DC converter (MDC). Within the DC converter section, there is a single inductor, two diodes, and N + 1 reverse-blocking transistors, where N represents the number of input ports in the multiport converter. In cases where the availability of reverse-blocking FETs is limited, a diode can be connected in series with a standard FET as an alternative solution. The distinctive advantages of the proposed MDC lie in its

FIGURE 1. Schematic of the integrated multiport converters system.

departure from conventional MDC designs. Unlike traditional MDCs that necessitate N inductors for N input sources, the proposed MDC employs just one inductor to accommodate any number of input sources. This feature holds the potential for achieving higher power density in the proposed MDC. Additionally, the incorporation of an additional input port only requires the inclusion of a single extra reverse-blocking FET.

The MDC offers a diverse range of unidirectional modes, including four modes that allow simultaneous power flow from two or more sources (e.g., V1 & V2, V2 & V3, V1 &  $V_3$ ,  $V_1$  &  $V_2$  &  $V_3$ ). Additionally, three modes enable independent power flow from each of the three sources  $(V_1 V_3$ ) to the DC link. Upon closer examination, the independent power flow from the sources exhibits similarities to the standard non-inverting buck-boost converter. In this mode, the switching period  $T_S$  is divided into two distinct periods:  $T_1$ for inductor charging and  $T_2$  for inductor discharging. The converter can operate in either the buck or boost mode in the independent power flow mode, depending on the duty ratio 'D' applied across the switches. Here, 'D' represents the ratio of the inductor charging time  $(T_1)$  to the total switching period  $(D = T_1/T_s)$ . Consequently, the conventional equations [38], [42] that describe the relationship between input and output voltage in a basic buck-boost converter also apply to this converter for independent power flow from the respective inputs to the output,  $V_{DC}$ .

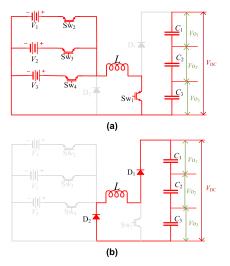

In the mode of simultaneous power transfer, as previously discussed, the operation of the MDC necessitates the concurrent supply of energy from two or more sources. In this paper, the MDC is examined in the context of three input sources, and the conduction modes during switching states and steady-state waveforms are illustrated in Figures 2 and 3, respectively. Within this mode, the inductor charging period denoted as  $T_1$ , is further subdivided into two or more subperiods, contingent upon the number of simultaneous input sources. Throughout the duration of  $T_1$ , switches  $S_{W1}$ ,  $S_{W2}$ , S<sub>W3</sub> and S<sub>W4</sub> are turned ON. On the other hand, during the initial subdivision of  $T_1$ , the inductor voltage corresponds to the highest source voltage, denoted as  $V_1$ . Consequently, the inductor charges at a rate of  $V_1/L$ . Once the first subdivision period of  $T_1$  concludes,  $S_{W2}$  is deactivated while  $S_{W3}$ ,  $S_{W4}$ and S<sub>W1</sub> remain activated. In the subsequent subdivision of

**FIGURE 2.** Path of current flow of the MDC in steady state CCM under simultaneous power transfer for inductor (a) charging and (b) discharging.

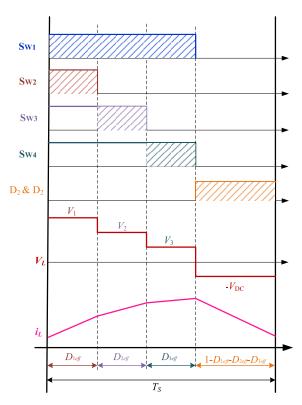

$T_1$ , the inductor voltage transitions to  $V_2$ , and the inductor continues to charge at a slope of  $V_2/L$ . During the third subdivision of  $T_1$ , only switches  $S_{W1}$  and  $S_{W4}$  will remain in the ON state, resulting in the inductor voltage equaling  $V_3$ . Consequently, the inductor continues to charge at a rate of  $V_3/L$ . This sequential charging process follows a similar pattern for an MDC with more than three inputs, where the subdivisions occur in decreasing order of the input voltage magnitudes. Upon completion of the inductor charging period, all active switches  $(S_{W1} - S_{W4})$  of the MDC transition to an OFF state, initiating the subsequent discharging period, denoted as  $T_2$ . Throughout  $T_2$ , the inductor (L) discharges through the capacitors  $(C_1 - C_3)$  to the DC bus via  $D_1$  and  $D_2$ . As a result, the voltage across the inductor becomes  $-V_o$ , and the discharge occurs with a gradient of  $-V_o/L$ . The resulting voltage across the inductor from each source is determined by multiplying the effective ON-time of the source by its corresponding voltage magnitude. Illustrated in Figure 3, the effective voltage values are as follows:  $D_{1eff}V_1$  for the first subdivision of the inductor charging period,  $D_{2eff}V_2$  for the second subdivision, and  $D_{3eff}V_3$  for the third subdivision.

To ensure efficient commutation of the switches during simultaneous power transfer, certain rules need to be followed to achieve the desired power transfer to the load. In the case of unequal voltages, if the input sources are arranged in ascending order of magnitudes  $(V_1 > V_2 > ... > V_N)$  for N input ports, the duty cycles of the switches  $(S_{W2}, S_{W3}, and$  $<math>S_{W4})$  controlling the input sources must be set in a manner that satisfies  $D_1 < D_2 < ... < D_N$ , and vice versa. This arrangement ensures the proper coordination of the switches to facilitate simultaneous power transfer. For,  $D_1 = D_{1eff}$ ,  $D_2 = D_{1eff} + D_{2eff}, ..., D_N = D_{1eff} + D_{2eff} + ... + D_{Neff}$ . But, in cases where the magnitudes of the input sources are equal  $(V_1 = V_2 = ... = V_N)$  for N input ports, the duty cycles of the PWM signals should be set such that  $D_1 = D_2 = ... =$  $D_N$  in order to achieve equal power delivery from all sources.

FIGURE 3. Steady state CCM waveforms of the MDC under simultaneous power transfer from the three sources to the dc link.

Then again, in cases where the desired power delivery from the sources is not equal, the values of  $D_1, D_2, \ldots, D_N$  can be determined in increasing order of magnitude based on the respective sources. Additionally, by applying the principle of volt-second balance to the steady-state waveform depicted in Figure 3, the relationship between the input sources and the output voltage can be described by equation (1) for Ninput sources and by equations (1) and (2) specifically for the three-input configuration. In cases where the input sources have equal magnitudes, and the duty cycles are equal, the relationship between the input and output voltage can be expressed as equation (3). Yet, if the input sources have equal voltages but unequal duty cycles, the relationship between the input and output voltage can be described by equation (4), where  $V_{in}$  is the input voltage and  $D_{max}$  represents the maximum duty cycle among  $D_1$  and  $D_2$ .

I

$$V_{O} = \frac{\sum_{i=1}^{N} \left( D_{(i)eff} V_{i} \right)}{1 - \sum_{i=1}^{N} D_{(i)eff}}$$

(1)

$$V_O = \frac{D_{1eff} V_1 + D_{2eff} V_2 + D_{3eff} V_3}{1 - D_{1eff} - D_{2eff} - D_{3eff}}$$

(2)

$$V_O = \frac{T_1}{T_2} V_{in} = \frac{D}{1 - D} V_{in}$$

(3)

$$V_o = \frac{D_{\max}}{1 - D_{\max}} V_{in} \tag{4}$$

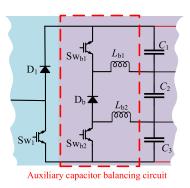

FIGURE 4. Schematic of the auxiliary circuit for capacitor balancing.

#### **B. MULTILEVEL INVERTER TOPOLOGY**

Figure 1 illustrates the MLI topology, which is indicated by the green shading. The MLI comprises of twelve unidirectional switches labelled as S1 to S12, along with three bidirectional switches identified as  $B_1$  to  $B_3$ . In order to streamline the gate-drive circuits, a common-emitter structure is implemented to configure the bidirectional switches. The MLI topology utilizes three dc-link capacitors to establish the dc-link configuration. Through the control of the inverter switches, the topology is capable of producing four unipolar voltage levels: 0, E/3, 2E/3, and E, which correspond to the pole voltages  $V_{A0}$ ,  $V_{B0}$ , and  $V_{C0}$ . By subtracting the adjacent pole voltages, the MLI can generate seven-level bipolar voltages in the line voltages  $V_{AB}$ ,  $V_{BC}$ , and  $V_{CA}$ . For instance, the voltage  $V_{AB}$  is created by subtracting the value of  $V_{B0}$ from  $V_{A0}$ , resulting in a seven-level voltage comprising of -E, -2E/3, -E/3, 0, E/3, 2E/3, and E. The operational modes and modulation techniques of the MLI topology are thoroughly discussed in [22], providing comprehensive insights into its functionality.

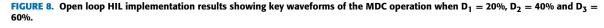

#### C. CAPACITOR VOLTAGE BALANCING AND CONTROL STRATEGY

Figure 5 presents the high-level control structure of the proposed MDC, indicating the different controllers utilised for the different sections of the MDC. Also highlighted in the control structure is the capacitor balance control strategy for both the circuit- and control-based schemes. In four-level inverter topologies, it is not uncommon to encounter capacitor voltage imbalances. This occurs when three capacitors are linked in series, dividing the dc-link voltage into three equal portions, as depicted in Figure 1. A comprehensive approach to analyze and address the issue of capacitor voltage imbalance in four-level topologies was detailed in [37]. The proposed configuration results in unequal currents flowing through the three capacitors in the DC link, namely  $I_{C1}$ ,  $I_{C2}$ , and  $I_{C3}$ . This current imbalance leads to a voltage disparity among the capacitors. Specifically, the current flowing through the middle capacitor,  $I_{C2}$ , is greater than the currents flowing through the other two capacitors,  $I_{C1}$  and  $I_{C3}$ , which are equal. As a result, there is an unequal discharge of energy among the capacitors  $C_1$  and  $C_3$  compared to  $C_2$ . Precisely,

FIGURE 5. Control structure of the proposed MDC.

$C_2$  discharges more rapidly until reaching zero, while the full DC-link voltage  $V_{dc}$  is equally distributed between  $C_1$  and  $C_3$ . This discrepancy in discharge causes an imbalance in the capacitor voltages, primarily due to the over-discharge of  $C_2$ . Hence, to achieve equilibrium among the capacitors,  $C_1$  and  $C_3$  can be balanced by regulating the voltage of  $C_2$ . Consequently, the three capacitor voltages,  $V_{C1}$ ,  $V_{C2}$ , and  $V_{C3}$ , become equal when  $V_{C2}$  is regulated to  $V_{dc}/3$ . A control-based voltage balancing approach known as the variable-carrier scheme (VCS) is employed for this purpose in previous studies [22], [37], which relies on control-based methods. The VCS approach comprises three essential components: the generation block for modulation signals, the block for carrier signals, and a PI controller. These components work together to generate modulation signals with variable third-harmonic injection and fixed carrier signals. The purpose of this signal generation is to regulate the voltage of  $C_2$ , ensuring it remains at  $V_{dc}/3$ .

Nevertheless, in this implementation, a more straightforward approach is adopted by incorporating an auxiliary circuitry for capacitor balancing. This auxiliary capacitor balancing circuit, depicted in Figure 4, involves the utilization of two inductors  $(L_{b1}, L_{b2})$  and three switches (a diode, D<sub>b</sub>, and two MOSFETs, S<sub>Wb1</sub>, S<sub>Wb2</sub>). The operation of S<sub>Wb1</sub> and S<sub>Wb2</sub> is orchestrated using a common pulse signal. When these switches are activated, the two inductors are charged and subsequently discharged through D<sub>b</sub>. This process ensures that the voltage of  $C_2$  does not drop to zero. To achieve this, a proportional controller is employed, selected through a heuristic approach, which determines the duty cycle of  $S_{Wb1}$  and  $S_{Wb2}$ . The controller ensures that the voltage of  $C_2$  is regulated to  $V_{dc}/3$ , while simultaneously maintaining the natural balance of  $C_1$  and  $C_3$  at  $V_{dc}/3$ . The use of a standard double-loop control strategy to regulate the

| Parameter                              | Value       | Unit          |

|----------------------------------------|-------------|---------------|

| Inductor (L)                           | 4           | mH            |

| Inductor $(L_{b1}=L_{b2})$             | 0.1         | mH            |

| Output capacitor ( $C_1 = C_2 = C_3$ ) | 9.4         | mF            |

| Voltage sources $(V_1/V_2/V_3)$        | 300/250/200 | V             |

| AC load $(R-L)$                        | 8.1 / 12.5  | $\Omega$ / mH |

#### TABLE 1. Parameters used in system verification.

multiple RESs has been introduced and explained in [38]. The stress on the different components of the MDC has been analysed separately in [22] for the MLI section and [38] for the multiple RES section, these are the converters from which the proposed MDC is synthesized.

#### **III. RESULTS**

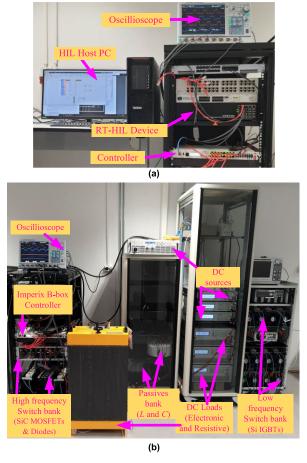

The validity of the suggested integrated converter system has been ascertained via numerical simulations and hardwarein-the-loop (HIL) implementation, utilizing the OPAL-RT's OP5700 device which is powered by a 64-bit virtex-7 FPGA. As depicted in Figure 6, the HIL and experimental setup employed for the validation process is presented, respectively, and the parameter values for each component utilized are shown in Table 1. Verification process was conducted under both open-loop and closed-loop conditions, and the outcomes were evaluated using numerical simulations, realtime HIL implementation and experimental verification. The key results of the verification process are included in this section.

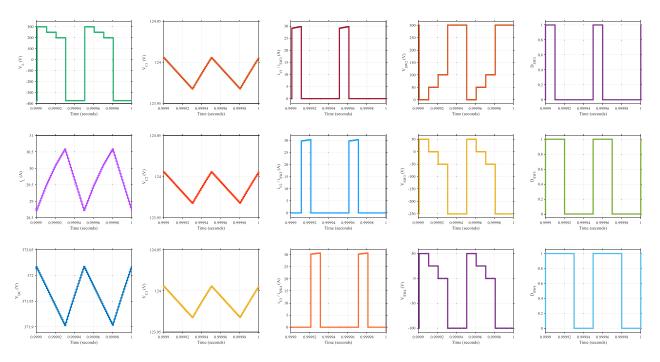

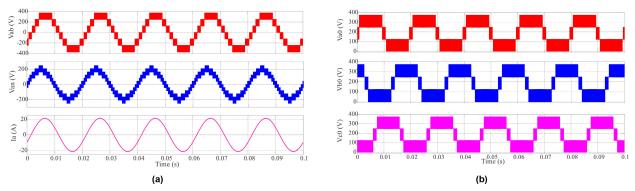

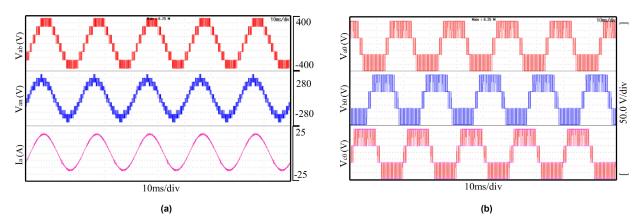

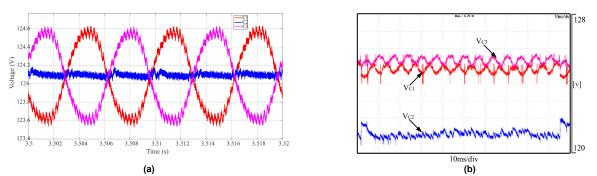

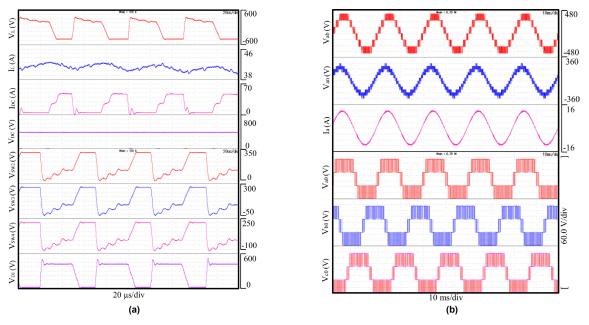

The simulation results in Figure 7 showcase the performance of the MDC in an open-loop configuration when the input voltages are set as  $V_1 = 300$  V,  $V_2 = 250$  V, and  $V_3 = 200$  V. The corresponding duty cycles applied to switches  $S_{W2}$  to  $S_{W4}$  are  $D_1 = 20\%$ ,  $D_2 = 40\%$  and  $D_3$ = 60% ( $D_{SW2}$  to  $D_{SW4}$ ), resulting in effective duty cycles of  $D_{1eff} = D_{2eff} = D_{3eff} = 0.2$ . In this scenario, the stress on the switches ( $V_{SW2}$  to  $V_{SW4}$ ), inductor ( $V_L$ ), and the current flowing through the switches ( $i_{SW2}$  to  $i_{SW4}$ ), which also represent the input currents from the sources ( $i_{V1}$  to  $i_{V3}$ ), are presented. Additionally, the voltage of the dc link  $(V_{DC})$  and the voltages across the three capacitors ( $V_{C1}$  to  $V_{C3}$ ) are also shown. The voltage of the dc link measures approximately 372 V and is evenly distributed across the three dc link capacitors, with each capacitor holding a voltage of around 124 V. The results obtained from the HIL implementation, as shown in Figure 8, align with the findings from the analytical simulation, confirming the accuracy and consistency of the system's performance. Additionally, the MLI stage operates using a level-shifted pulse width modulation (LS-PWM) scheme, which is extensively explained in [22]. Figures 9 and 10 showcase the outcomes of the simulation and HIL implementation of the MLI stage. In both cases, the MLI stage was configured to generate seven-level output voltages at a frequency of 50 Hz. It is noteworthy that the simulation and HIL results agree, providing further validation of the MLI's performance and functionality.

FIGURE 6. Integrated converter system validation on (a) in-house HIL platform and (b) the experimental validation platform.

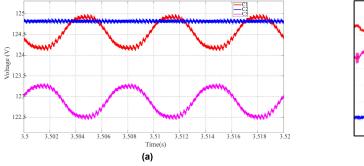

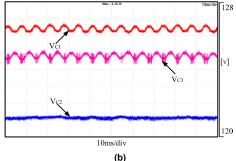

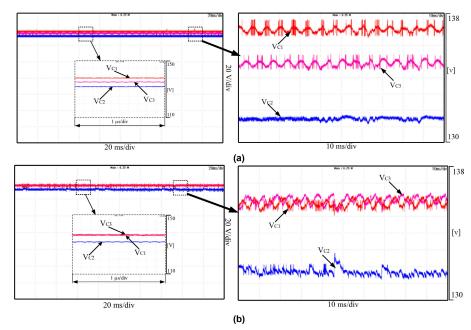

In order to validate the voltage balancing across the dc link capacitors, both the control-based voltage balancing technique and the circuit-based voltage balancing were applied in both simulation and the HIL platform. The outcomes for each technique can be observed in Figures 11 and 12, respectively. These results serve to confirm the effectiveness of both voltage balancing approaches in maintaining a balanced voltage distribution across the dc link capacitors. The controller parameters of the control-based voltage balancing technique were determined using a heuristic approach, as detailed in [22]. As depicted in Figure 11 (a), the controller successfully maintains a stable steady state with the voltage across C<sub>2</sub>, V<sub>C2</sub>, regulated at approximately 124.8 V. Meanwhile, C<sub>1</sub> and C<sub>3</sub> exhibit natural balancing tendencies, distributing the remaining 247 V. It is worth noting that some oscillations are observed in the simulation results. Likewise, in the HIL implementation results shown in Figure 11 (b), the control-based voltage balancing technique successfully regulates V<sub>C2</sub> to approximately 121 V. Meanwhile,  $C_1$  and  $C_3$  exhibit natural balancing tendencies, distributing the remaining 251 V. Oscillations are also observed in this scenario. On the other hand, the circuit-based capacitor balancing technique employs a basic proportional controller to regulate the active switches (Swb1 and Swb2) of the

### IEEE Access

FIGURE 7. Open loop simulation results showing key waveforms of the MDC operation when  $D_1 = 20\%$ ,  $D_2 = 40\%$  and  $D_3 = 60\%$ .

**FIGURE 9.** Simulation results of the MLI when the MDC duty is  $D_1 = 20\%$ ,  $D_2 = 40\%$  and  $D_3 = 60\%$  showing (a) output current and voltage waveforms and (b) the pole voltages.

auxiliary capacitor balancing circuit. These switches operate with identical duty cycles, as determined heuristically. Figure 12 (a) presents the simulation outcome, demonstrating the successful achievement of capacitor voltage balancing through the implementation of the auxiliary circuit-based technique. Notably, this technique exhibits superior accuracy compared to the control-based technique shown in Figure 11 (a).  $V_{C2}$  is effectively regulated to approximately 124.1 V,

**FIGURE 10.** HIL implementation results of the MLI when the MDC duty is  $D_1 = 20\%$ ,  $D_2 = 40\%$  and  $D_3 = 60\%$  showing (a) output current and voltage waveforms and (b) the pole voltages.

FIGURE 11. Control-based dc link capacitor voltage balancing showing (a) simulation and (b) HIL implementation results.

FIGURE 12. Auxiliary circuit-based dc link capacitor voltage balancing showing (a) simulation and (b) HIL implementation results.

while the remaining voltage of 248 V is equally distributed between  $C_1$  and  $C_3$ . Oscillations, as observed earlier in Figure 11, are also present in this simulation. Additionally, Figure 12 (b) showcases the HIL implementation outcome, which aligns consistently with the simulation result depicted in Figure 12 (a).  $V_{C2}$  is effectively regulated to approximately 121 V, while the remaining voltage of 251 V is equally distributed between  $C_1$  and  $C_3$ . Some oscillations are observed in this HIL implementation result as well. Comparing the HIL implementation results of the control-based technique displayed in Figure 11 (b) and the circuit-based technique illustrated in Figure 12 (b), it becomes evident that the latter achieves a more balanced distribution of the leftover voltage between  $C_1$  and  $C_3$  after  $V_{C2}$  is controlled to the required value. Moreover, the circuit-based approach necessitates additional components but demands less controller effort, whereas the control-based technique entails a complex controller without the need for extra components. Therefore, a trade-off between control complexity and component count must be carefully considered when deciding between these two techniques.

Furthermore, the closed-loop operation of the integrated converter system was implemented using the MDC, with the objective of regulating VDC to a target value of 400 V during the HIL implementation. The closed-loop strategy employed for MDCs, as detailed in [42], was adopted for this specific configuration. The PI control variables were heuristically chosen to attain the desired dynamic

FIGURE 13. Closed loop HIL validation results showing (a) key waveforms of the MDC operation and (b) output current and voltage waveforms and the pole voltages.

FIGURE 14. HIL execution results under closed operation of the MDC for (a) control-based dc link capacitor voltage balancing and (b) auxiliary circuit-based dc link capacitor voltage balancing.

performance characteristics. The results obtained from the closed-loop operation of the MDC section in the integrated converter system are illustrated in Figure 13. This figure showcases important measurements obtained during the operation. Additionally, a comparative analysis was conducted between the control-based and circuit-based techniques for balancing the voltage across the dc link capacitors under closed-loop conditions. The comparative results are presented in Figure 14. Once more, the circuit-based voltage balancing technique demonstrates a slightly superior performance in achieving an equal distribution of the dc link voltage

among the three capacitors, without the need for the complex controller employed in the control-based technique. These findings provide further validation for the proposed integrated converter system, which effectively integrates multiple DC sources into both DC and AC grids.

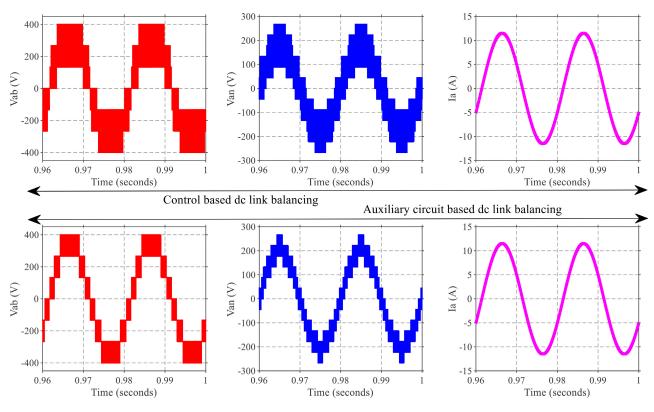

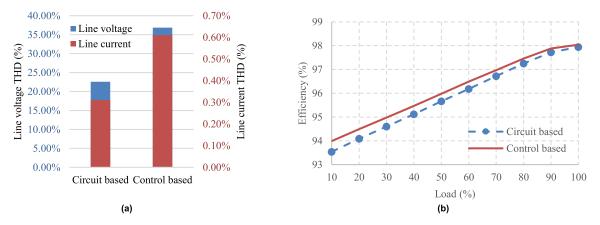

Furthermore, Figure 15 presents a comparison of the auxiliary circuit-based DC link capacitor balancing and the control-based VCS method to further highlight the differences and advantages of using the circuit-based approach. The phase voltage, line current and voltage is presented in Figure 15 for both cases. The auxiliary circuit method

FIGURE 15. Comparison of control and auxiliary circuit-based DC link balancing showing Line and phase voltages and line currents.

FIGURE 16. Analysis of (a) THD and (b) Efficiency of the MDC at 6 kW load.

(bottom row) produces better-quality waveforms than the control based balancing method shown in the top row of Figure 15. This is further emphasized by the comparison of the THDs presented in Figure 16 (a), comparing the line voltage and currents. The THD of the circuit based balancing method's line voltage and current is 22.56% and 0.31%, respectively, that is about 40% and 50% less than that of the VCS control-based method which is 36.85% and 0.61%, respectively. Consequently, the circuit-based method results in lower THD although at higher component count. It is worthy of note that the THD of currents are significantly low for both cases because of the inductive load. Further, to analyse the efficiency of the proposed MDC as presented in Figure 16

(b), the power losses  $(P_L)$  in MDC can be estimated using (5), consisting of the inductor and transformer winding  $(P_W)$  and core  $(P_C)$  losses [43], capacitor losses  $(P_{Cap})$ , MOSFET switching  $(P_{swMOS})$  and conduction  $(P_{onMOS})$  losses [44], and the losses in the diode  $(P_D)$ . Where  $T_S$  is the switching period,  $R_{ESRL}$  is the inductor's equivalent series resistance (ESR),  $\hat{i}_L$  is the inductor average current,  $\Delta i_L$  is the inductor ripple current, K,  $\beta \& \alpha$  are Steinmetz parameters,  $R_{ESRC}$  is the capacitor ESR,  $V_{DS}$  is the MOSFET drain to source voltage,  $i_{DS}$  is the MOSFET drain to source current,  $t_{on}\& t_{off}$  is the MOSFET ON and OFF time,  $R_{DSon}$  is the MOSFET on state resistance, D is its respective duty cycle,  $V_F$  and  $i_F$  are the diodes' forward voltage and current respectively. From

| Param         | eters | $T_1$ [30] | $T_2$ [27] | $T_3$ [28] | T <sub>4</sub> -A [31] | T <sub>4</sub> -B [31] | T <sub>5</sub> [29] | Proposed                     |

|---------------|-------|------------|------------|------------|------------------------|------------------------|---------------------|------------------------------|

| Part<br>Count | S     | 26         | 27         | 14         | 36                     | 48                     | 27                  | 22                           |

|               | D     | 2          | 0          | 2          | 0                      | 0                      | 0                   | 2                            |

|               | L     | 2          | 0          | 2          | 3                      | 6                      | 0                   | 1                            |

|               | С     | 4          | 3          | 3          | 0                      | 0                      | 5                   | 3                            |

|               | Т     | 34         | 30         | 21         | 39                     | 54                     | 32                  | 28                           |

| No. of inpu   | its   | 1          | 3          | 1          | 6                      | 6                      | 1                   | Ν                            |

| IPF           |       | NA         | No         | NA         | No                     | No                     | NA                  | Yes                          |

| SPF           |       | NA         | Yes        | NA         | Yes                    | Yes                    | No                  | Yes                          |

| Isolated in   | puts? | No         | Yes        | No         | Yes                    | Yes                    | No                  | No                           |

| No of levels  |       | 4          | 5          | 4          | 5                      | 5                      | 7                   | 4                            |

| Boosting fa   | actor | 3          | 2          | 3          | (1-D):1                | (1-D):2                | 1.5                 | $1/(1-\sum_{i}^{N}D_{ieff})$ |

| Buck-Boos     | st?   | Boost      | Boost      | Boost      | Boost                  | Boost                  | Boost               | Buck-Boost                   |

TABLE 2. Comparison of the proposed converter system with related converters.

the efficiency results in Figure 16 (b), the MDC has a slightly higher efficiency if the VCS capacitor balancing scheme is adopted. This is due to the losses in the additional circuitry required in the auxiliary circuit-based capacitor balancing scheme. Overall, the efficiency of the MDC over the entire operating range is well above 90% for both VCS and the auxiliary circuit-based capacitor balancing scheme.

$$P_{L} \approx \begin{cases} \underbrace{\frac{1}{T_{S}} \int_{0}^{T_{S}} R_{ESR}\left(\hat{i}_{L}^{2} + \frac{\Delta i_{L}^{2}}{12}\right) + \underbrace{K \Delta i_{L}^{\beta} F_{SW}^{\alpha}}_{P_{C}}}_{P_{C}} \\ + \underbrace{R_{ESRC} \left(\frac{\Delta i_{L}}{2\sqrt{3}}\right)^{2}}_{P_{Cap}} + \underbrace{\frac{1}{2} V_{DS} i_{DS} F_{SW} \left(t_{on} + t_{off}\right)}_{P_{swMOS}} \\ + \underbrace{R_{DSon} \hat{i}_{DS}^{2} D}_{P_{onMOS}} + \underbrace{\frac{1}{T_{S}} \int_{0}^{T_{S}} V_{F} \hat{i}_{F}^{2}}_{P_{D}} \end{cases} \end{cases}$$

$$(5)$$

#### **IV. COMPARISON WITH RELATED TOPOLOGIES**

Table 2 compares the proposed converter system with related existing converters to highlight the novelty. The selected converters are labelled topologies,  $T_1 - T_5$  [27], [28], [29], [30], [31], as they are of similar structure to the converter system proposed in this paper, since the single phase topologies were converted to their three phase configurations. Firstly, by examining their component counts, only  $T_3$  has a lower component count than the proposed converter has three input ports, while the proposed converter has three input ports. This is a similar case for  $T_1$  and  $T_5$  which have only a single input source as well, and a higher component count than the proposed converter.

In the case of  $T_2$  and  $T_4$  which have multiple number of RES input ports for three phases, independent power flow cannot be carried out arbitrarily from any of the input ports. Further, the voltage level of the input ports must be matched for these converters to perform optimally in simultaneous

power transfer mode. Meanwhile, the proposed converter can perform arbitrary independent transfer of power from the RESs to the AC output and simultaneous power transfer under varying voltages at the RESs. In addition to this, in  $T_2$  and  $T_4$ with multiple inputs, these inputs need to be isolated, thus, an isolation transformer is required. While in the proposed topology, the RESs do not need to be isolated, and so the power density is higher and component count is kept lower than the converters in  $T_2$  and  $T_4$ . Furthermore, the proposed converter system can buck and boost the input voltages while the counterparts can only boost the input. It also has the highest boosting factor of all the converters compared, a testament of the high voltage gain obtainable when the proposed converter system is applied for RES to AC grid integration.

#### **V. CONCLUSION**

This research introduced an innovative converter system that combines a new multiport DC-DC converter and a multilevel inverter topology. The new multiport DC-DC converter enables the seamless integration of various renewable energy sources, including photovoltaics, wind power, and fuel cell systems, into both DC and AC buses. Notably, the proposed configuration offers a simplified design with reduced components and complexities compared to existing approaches documented in the literature. The analysis of the proposed integrated converter system was performed considering three input sources operating in a simultaneous power flow configuration. Additionally, two different techniques for dc link capacitor voltage balancing were compared. The circuit-based balancing technique demonstrated a notable advantage, exhibiting lower total harmonic distortion compared to the control-based voltage balancing technique. The validity of the proposed integrated converter system was confirmed through numerical simulations and experimental testing on an FPGA-based high-fidelity hardware-in-the-loop implementation platform. The system's performance was evaluated in both open-loop and closed-loop operations to ensure its effectiveness and reliability.

#### REFERENCES

B. K. Bose, "Global warming: Energy, environmental pollution, and the impact of power electronics," *IEEE Ind. Electron. Mag.*, vol. 4, no. 1, pp. 6–17, Mar. 2010, doi: 10.1109/MIE.2010.935860.

- [2] N. Hou, L. Ding, P. Gunawardena, T. Wang, Y. Zhang, and Y. W. Li, "A partial power processing structure embedding renewable energy source and energy storage element for islanded DC microgrid," *IEEE Trans. Power Electron.*, vol. 38, no. 3, pp. 4027–4039, Mar. 2023, doi: 10.1109/TPEL.2022.3221349.

- [3] S. M. Taheri, A. Baghramian, and S. A. Pourseyedi, "A novel highstep-up SEPIC-based nonisolated three-port DC–DC converter proper for renewable energy applications," *IEEE Trans. Ind. Electron.*, vol. 70, no. 10, pp. 10114–10122, Oct. 2023, doi: 10.1109/TIE.2022.3220909.

- [4] K. Jia, Z. Yang, Y. Fang, T. Bi, and M. Sumner, "Influence of inverter-interfaced renewable energy generators on directional relay and an improved scheme," *IEEE Trans. Power Electron.*, vol. 34, no. 12, pp. 11843–11855, Dec. 2019, doi: 10.1109/TPEL.2019.2904715.

- [5] F. Wu, X. Li, F. Feng, and H. B. Gooi, "Multi-topology-mode gridconnected inverter to improve comprehensive performance of renewable energy source generation system," *IEEE Trans. Power Electron.*, vol. 32, no. 5, pp. 3623–3633, May 2017, doi: 10.1109/TPEL.2016.2589974.

- [6] L. B. G. Campanhol, S. A. O. da Silva, A. A. de Oliveira, and V. D. Bacon, "Power flow and stability analyses of a multifunctional distributed generation system integrating a photovoltaic system with unified power quality conditioner," *IEEE Trans. Power Electron.*, vol. 34, no. 7, pp. 6241–6256, Jul. 2019, doi: 10.1109/TPEL.2018.2873503.

- [7] C. Zhang, X. Dou, L. Wang, Y. Dong, and Y. Ji, "Distributed cooperative voltage control for grid-following and grid-forming distributed generators in islanded microgrids," *IEEE Trans. Power Syst.*, vol. 38, no. 1, pp. 589–602, Jan. 2023, doi: 10.1109/TPWRS.2022.3158306.

- [8] J. Zhang, B. Sun, and D. Zhao, "A novel event-triggered secondary control strategy for distributed generalized droop control in microgrid considering time delay," *IEEE Trans. Power Electron.*, vol. 38, no. 5, pp. 5963–5978, May 2023, doi: 10.1109/TPEL.2023.3241063.

- [9] S. Hasan and V. Agarwal, "A voltage support scheme for distributed generation with minimal phase current under asymmetrical grid faults," *IEEE Trans. Ind. Electron.*, vol. 70, no. 10, pp. 10261–10270, Oct. 2023, doi: 10.1109/TIE.2022.3219045.

- [10] T. Strasser, F. Andrén, J. Kathan, C. Cecati, C. Buccella, P. Siano, P. Leitão, G. Zhabelova, V. Vyatkin, P. Vrba, and V. Marík, "A review of architectures and concepts for intelligence in future electric energy systems," *IEEE Trans. Ind. Electron.*, vol. 62, no. 4, pp. 2424–2438, Apr. 2015, doi: 10.1109/TIE.2014.2361486.

- [11] T. Dragicevic, X. Lu, J. C. Vasquez, and J. M. Guerrero, "DC microgrids— Part I: A review of control strategies and stabilization techniques," *IEEE Trans. Power Electron.*, vol. 31, no. 7, pp. 4876–4891, Jul. 2016, doi: 10.1109/TPEL.2015.2478859.

- [12] R. Panigrahi, S. K. Mishra, S. C. Srivastava, A. K. Srivastava, and N. N. Schulz, "Grid integration of small-scale photovoltaic systems in secondary distribution network—A review," *IEEE Trans. Ind. Appl.*, vol. 56, no. 3, pp. 3178–3195, May 2020, doi: 10.1109/TIA.2020.2979789.

- [13] J. Schaumburg, J. Kuprat, M. Langwasser, and M. Liserre, "Efficiency optimization via mission profile-based power routing by design of hybrid grid connecting converter architecture," *IEEE Open J. Power Electron.*, vol. 4, pp. 128–136, 2023, doi: 10.1109/OJPEL.2023.3241778.

- [14] M. Trabelsi, A. N. Alquennah, and H. Vahedi, "Review on single-DCsource multilevel inverters: Voltage balancing and control techniques," *IEEE Open J. Ind. Electron. Soc.*, vol. 3, pp. 711–732, 2022, doi: 10.1109/OJIES.2022.3221015.

- [15] M. Vijeh, M. Rezanejad, E. Samadaei, and K. Bertilsson, "A general review of multilevel inverters based on main submodules: Structural point of view," *IEEE Trans. Power Electron.*, vol. 34, no. 10, pp. 9479–9502, Oct. 2019, doi: 10.1109/TPEL.2018.2890649.

- [16] Y. Y. Syasegov, M. Farhangi, R. Barzegarkhoo, Y. P. Siwakoti, L. Li, D. D. Lu, R. P. Aguilera, and J. Pou, "A 5-level HERIC active-clamped inverter with full reactive power capability for grid-connected applications," *IEEE Open J. Ind. Electron. Soc.*, vol. 4, pp. 135–148, 2023, doi: 10.1109/OJIES.2023.3271637.

- [17] N. Tak, S. K. Chattopadhyay, and C. Chakraborty, "Single-sourced double-stage multilevel inverter for grid-connected solar PV systems," *IEEE Open J. Ind. Electron. Soc.*, vol. 3, pp. 561–581, 2022, doi: 10.1109/OJIES.2022.3206352.

- [18] A. Salem, H. Van Khang, K. G. Robbersmyr, M. Norambuena, and J. Rodriguez, "Voltage source multilevel inverters with reduced device count: Topological review and novel comparative factors," *IEEE Trans. Power Electron.*, vol. 36, no. 3, pp. 2720–2747, Mar. 2021, doi: 10.1109/TPEL.2020.3011908.

- [19] P. Omer, J. Kumar, and B. S. Surjan, "A review on reduced switch count multilevel inverter topologies," *IEEE Access*, vol. 8, pp. 22281–22302, 2020, doi: 10.1109/ACCESS.2020.2969551.

- [20] A. Poorfakhraei, M. Narimani, and A. Emadi, "A review of modulation and control techniques for multilevel inverters in traction applications," *IEEE Access*, vol. 9, pp. 24187–24204, 2021, doi: 10.1109/ACCESS.2021.3056612.

- [21] A. Poorfakhraei, M. Narimani, and A. Emadi, "A review of multilevel inverter topologies in electric vehicles: Current status and future trends," *IEEE Open J. Power Electron.*, vol. 2, pp. 155–170, 2021, doi: 10.1109/OJPEL.2021.3063550.

- [22] A. Salem, H. Van Khang, and K. G. Robbersmyr, "Four-level threephase inverter with reduced component count for low and medium voltage applications," *IEEE Access*, vol. 9, pp. 35151–35163, 2021, doi: 10.1109/ACCESS.2021.3062110.

- [23] V. Sidorov, A. Chub, D. Vinnikov, and F. Z. Peng, "Survey of topology morphing control techniques for performance enhancement of galvanically isolated DC–DC converters," *IEEE Open J. Ind. Electron. Soc.*, vol. 3, pp. 751–777, 2022, doi: 10.1109/OJIES.2022.3225265.

- [24] M. I. Marei, B. N. Alajmi, I. Abdelsalam, and N. A. Ahmed, "An integrated topology of three-port DC–DC converter for PV-battery power systems," *IEEE Open J. Ind. Electron. Soc.*, vol. 3, pp. 409–419, 2022, doi: 10.1109/OJIES.2022.3182977.

- [25] A. Bughneda, M. Salem, E. Hossain, D. Ishak, and N. Prabaharan, "Design considerations and performance investigation of a five-level cascaded multilevel LLC boost DC–DC converter," *IEEE Access*, vol. 11, pp. 40441–40456, 2023, doi: 10.1109/ACCESS.2023.3249229.

- [26] S. Jakkula, N. Jayaram, S. V. K. Pulavarthi, Y. R. Shankar, and J. Rajesh, "A generalized high gain multilevel inverter for small scale solar photovoltaic applications," *IEEE Access*, vol. 10, pp. 25175–25189, 2022, doi: 10.1109/ACCESS.2022.3152771.

- [27] N. Sandeep, J. S. M. Ali, U. R. Yaragatti, and K. Vijayakumar, "A selfbalancing five-level boosting inverter with reduced components," *IEEE Trans. Power Electron.*, vol. 34, no. 7, pp. 6020–6024, Jul. 2019, doi: 10.1109/TPEL.2018.2889785.

- [28] S. Dhara and V. T. Somasekhar, "An integrated semi-double stagebased multilevel inverter with voltage boosting scheme for photovoltaic systems," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 3, pp. 2326–2339, Sep. 2020, doi: 10.1109/JESTPE.2019.2955729.

- [29] S. S. Lee, C. S. Lim, and K.-B. Lee, "Novel active-neutral-pointclamped inverters with improved voltage-boosting capability," *IEEE Trans. Power Electron.*, vol. 35, no. 6, pp. 5978–5986, Jun. 2020, doi: 10.1109/TPEL.2019.2951382.

- [30] S. Dhara and V. T. Somasekhar, "A nine-level transformerless boost inverter with leakage current reduction and fractional direct power transfer capability for PV applications," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 10, no. 6, pp. 7938–7949, Dec. 2022, doi: 10.1109/JESTPE.2021.3074701.

- [31] Q. Huang, A. Q. Huang, R. Yu, P. Liu, and W. Yu, "High-efficiency and high-density single-phase dual-mode cascaded buck-boost multilevel transformerless PV inverter with GaN AC switches," *IEEE Trans. Power Electron.*, vol. 34, no. 8, pp. 7474–7488, Aug. 2019, doi: 10.1109/TPEL.2018.2878586.

- [32] M. T. Elrais, M. Safayatullah, and I. Batarseh, "Generalized architecture of a GaN-based modular multiport multilevel flying capacitor converter," *IEEE Trans. Power Electron.*, vol. 38, no. 8, pp. 9818–9838, Aug. 2023, doi: 10.1109/TPEL.2023.3269800.

- [33] S. R. Khasim, C. Dhanamjayulu, and S. M. Muyeen, "A single inductor multi-port power converter for electric vehicle applications," *IEEE Access*, vol. 11, pp. 3367–3385, 2023, doi: 10.1109/ACCESS.2023.3234105.

- [34] M. Rouhani and G. J. Kish, "Multiport DC–DC–AC modular multilevel converters for hybrid AC/DC power systems," *IEEE Trans. Power Del.*, vol. 35, no. 1, pp. 408–419, Feb. 2020, doi: 10.1109/TPWRD.2019.2927324.

- [35] Y. Li and G. J. Kish, "Comparative assessment of multi-port MMCs for high-power applications," *IEEE Access*, vol. 10, pp. 22049–22060, 2022, doi: 10.1109/ACCESS.2022.3152536.

- [36] H. Wu, L. Zhu, and F. Yang, "Three-port-converter-based single-phase bidirectional AC–DC converter with reduced power processing stages and improved overall efficiency," *IEEE Trans. Power Electron.*, vol. 33, no. 12, pp. 10021–10026, Dec. 2018, doi: 10.1109/TPEL.2018.2824242.

- [37] J. Chen and C. Wang, "Dual T-type four-level converter," *IEEE Trans. Power Electron.*, vol. 35, no. 6, pp. 5594–5600, Jun. 2020, doi: 10.1109/TPEL.2019.2957699.

### IEEE Access

- [38] I. Ninma Jiya, H. Van Khang, N. Kishor, and R. M. Ciric, "Novel family of high-gain nonisolated multiport converters with bipolar symmetric outputs for DC microgrids," *IEEE Trans. Power Electron.*, vol. 37, no. 10, pp. 12151–12166, Oct. 2022, doi: 10.1109/TPEL.2022.3176688.

- [39] I. N. Jiya, A. Salem, and H. Van Khang, "Integrated multiport DC–DC and multilevel converters for energy sources," in *Proc. IEEE Ind. Appl. Soc. Annu. Meeting (IAS)*, Oct. 2022, pp. 1–7, doi: 10.1109/IAS54023.2022.9939764.

- [40] H. Chalangar, T. Ould-Bachir, K. Sheshyekani, and J. Mahseredjian, "Methods for the accurate real-time simulation of high-frequency power converters," *IEEE Trans. Ind. Electron.*, vol. 69, no. 9, pp. 9613–9623, Sep. 2022, doi: 10.1109/TIE.2021.3114706.

- [41] Z. Sun and S. Bae, "Multiple-input soft-switching DC–DC converter to connect renewable energy sources in a DC microgrid," *IEEE Access*, vol. 10, pp. 128380–128391, 2022, doi: 10.1109/ACCESS.2022.3227439.

- [42] I. N. Jiya, A. Salem, H. Van Khang, N. Kishor, and R. Ciric, "Novel multisource DC–DC converter for all-electric hybrid energy systems," *IEEE Trans. Ind. Electron.*, vol. 69, no. 12, pp. 12934–12945, Dec. 2022, doi: 10.1109/TIE.2021.3131871.

- [43] H. Matsumori, T. Shimizu, X. Wang, and F. Blaabjerg, "A practical core loss model for filter inductors of power electronic converters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 6, no. 1, pp. 29–39, Mar. 2018, doi: 10.1109/JESTPE.2017.2761127.

- [44] L. Keuck, N. Jabbar, F. Schafmeister, and J. Böeker, "Switching loss characterization of wide band-gap devices by an indirect identification methodology," in *Proc. 20th Eur. Conf. Power Electron. Appl. (EPE ECCE Europe)*, Riga, Latvia, Sep. 2018, pp. 1–10.

**IMMANUEL N. JIYA** (Member, IEEE) received the B.Eng. degree in electrical and electronics engineering from the Federal University of Technology Minna, Minna, Nigeria, in 2016, the M.Eng. degree in electrical and electronic engineering from North-West University, Potchefstroom, South Africa, in 2019, and the Ph.D. degree in renewable energy from the Faculty of Engineering and Science, University of Agder, Grimstad, Norway, in 2023.

From July 2022 to January 2023, he was a Guest Ph.D. Researcher with the Electronic and Intelligent (ELITE) Grid Research Laboratory, Department of Electrical and Computer Engineering, University of Alberta, Edmonton, Canada. His research interests include hardware-in-the-loop (HIL) and experimental design and control of new converter topologies and their applications to renewable energy and microgrid systems.

**AHMED SALEM** (Associate Member, IEEE) received the B.Sc. and M.Sc. degrees in electrical engineering from the Faculty of Engineering and Technology, Aswan University, Aswan, Egypt, in 2012 and 2016, respectively, and the Ph.D. degree in renewable energy from the Faculty of Engineering and Science, University of Agder, Grimstad, Norway, in 2021. His research interests include new converter topologies and applications of multilevel inverters to renewable energy and microgrid systems.

**HUYNH VAN KHANG** received the B.Sc. degree in electrical engineering from the Ho Chi Minh City University of Technology, Ho Chi Minh City, Vietnam, in 2002, the M.Sc. degree in electrical engineering from Pusan National University, Busan, South Korea, in 2008, and the D.Sc. (Tech.) degree in electrical engineering from Aalto University, Espoo, Finland, in 2012.

He was an Associate Professor of electrical power engineering with the University of Agder,

Grimstad, Norway, from 2013 to 2019, where he is currently a Professor with the Department of Engineering Sciences. His research interests include electrical machines, condition-based maintenance, and applied power electronics.

**RAIMONDAS POMARNACKI** defended his Ph.D. dissertation entitled "Investigation of Electrodynamic Retardn Devices Using Parallel Computer Systems," in 2011. He has published 32 scientific articles, 17 of which are in ISI Web of Science referenced databases with citation index. He was the Leader of two research and development projects and a senior participant in five others. He participated in over 11 international conferences in abroad and Lithuania. He focuses

on the research and design of electromagnetic devices for various purposes, including antennas, and in the fields of electrical engineering and signal processing. He also has significant experience in software development for the embedded systems for controlling, monitoring electrical, and electronic devices. Furthermore, for a few years, he created and implemented various signal processing and neural networks methods algorithms to analyze, detect, and control various behaviors for the autonomous vehicles as UAV, motor control, and electromagnetic devices, such as antennas.